**Preliminary User's Manual**

# **V850E/ME2**<sup>™</sup>

# **32-Bit Single-Chip Microcontroller**

Hardware

μ**PD703111**

Document No. U16031EJ2V1UD00 (2nd edition) Date Published May 2003 N CP(K)

© NEC Electronics Corporation 2002 Printed in Japan [MEMO]

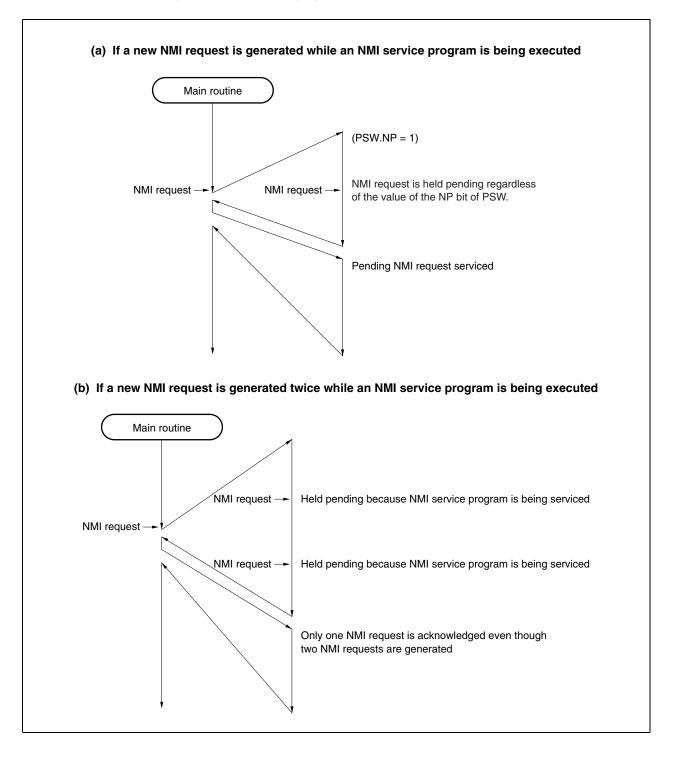

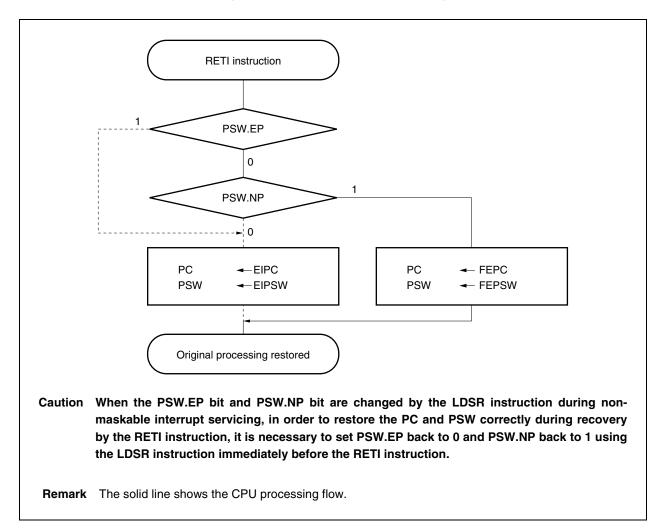

#### **①** PRECAUTION AGAINST ESD FOR SEMICONDUCTORS

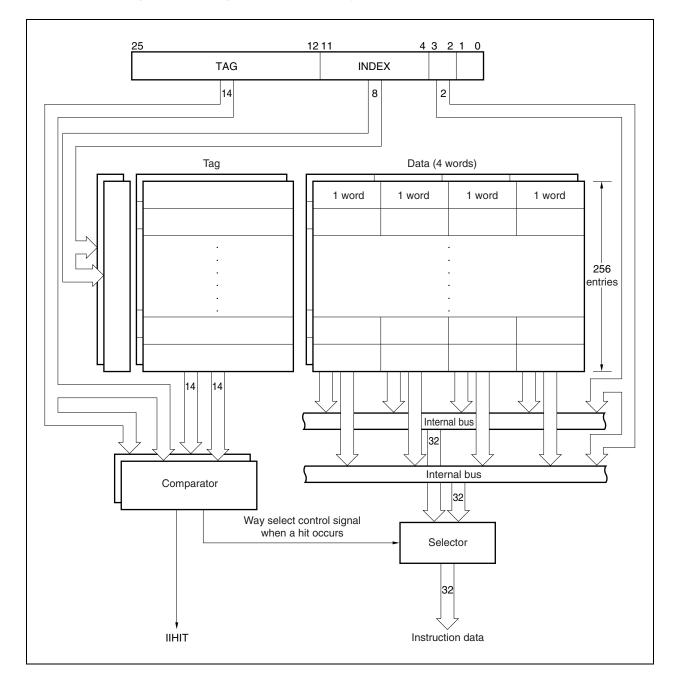

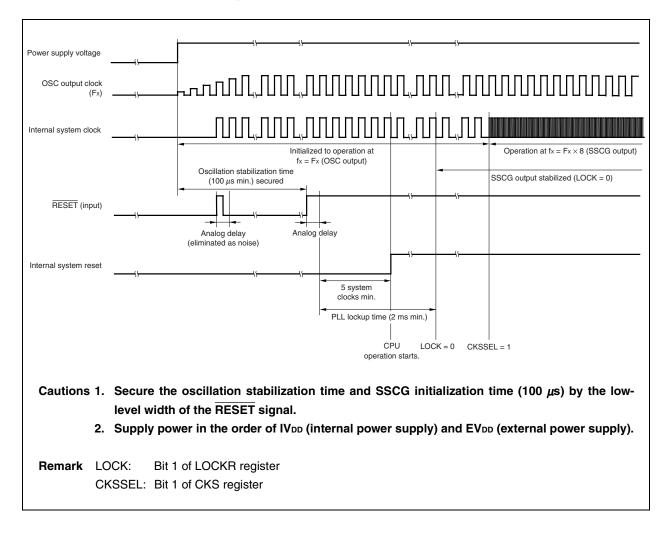

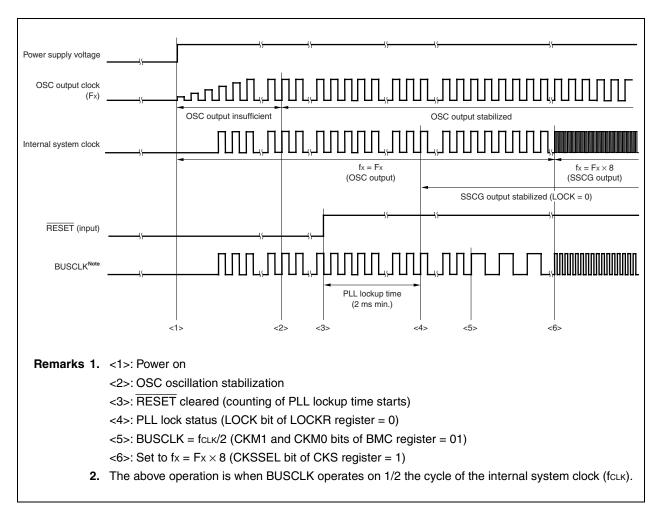

#### Note:

Strong electric field, when exposed to a MOS device, can cause destruction of the gate oxide and ultimately degrade the device operation. Steps must be taken to stop generation of static electricity as much as possible, and quickly dissipate it once, when it has occurred. Environmental control must be adequate. When it is dry, humidifier should be used. It is recommended to avoid using insulators that easily build static electricity. Semiconductor devices must be stored and transported in an anti-static container, static shielding bag or conductive material. All test and measurement tools including work bench and floor should be grounded. The operator should be grounded using wrist strap. Semiconductor devices must not be touched with bare hands. Similar precautions need to be taken for PW boards with semiconductor devices on it.

#### **②** HANDLING OF UNUSED INPUT PINS FOR CMOS

#### Note:

No connection for CMOS device inputs can be cause of malfunction. If no connection is provided to the input pins, it is possible that an internal input level may be generated due to noise, etc., hence causing malfunction. CMOS devices behave differently than Bipolar or NMOS devices. Input levels of CMOS devices must be fixed high or low by using a pull-up or pull-down circuitry. Each unused pin should be connected to VDD or GND with a resistor, if it is considered to have a possibility of being an output pin. All handling related to the unused pins must be judged device by device and related specifications governing the devices.

#### **③** STATUS BEFORE INITIALIZATION OF MOS DEVICES

#### Note:

Power-on does not necessarily define initial status of MOS device. Production process of MOS does not define the initial operation status of the device. Immediately after the power source is turned ON, the devices with reset function have not yet been initialized. Hence, power-on does not guarantee out-pin levels, I/O settings or contents of registers. Device is not initialized until the reset signal is received. Reset operation must be executed immediately after power-on for devices having reset function.

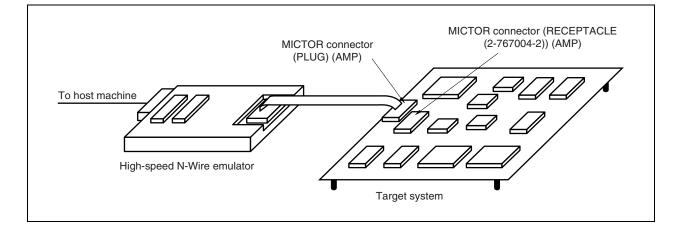

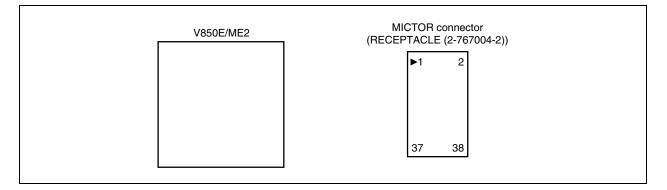

V850 Series and V850E/ME2 are trademarks of NEC Electronics Corporation.

- The information contained in this document is being issued in advance of the production cycle for the product. The parameters for the product may change before final production or NEC Electronics Corporation, at its own discretion, may withdraw the product prior to its production.

- Not all products and/or types are available in every country. Please check with an NEC Electronics sales representative for availability and additional information.

- No part of this document may be copied or reproduced in any form or by any means without the prior written consent of NEC Electronics. NEC Electronics assumes no responsibility for any errors that may appear in this document.

- NEC Electronics does not assume any liability for infringement of patents, copyrights or other intellectual property rights of third parties by or arising from the use of NEC Electronics products listed in this document or any other liability arising from the use of such products. No license, express, implied or otherwise, is granted under any patents, copyrights or other intellectual property rights of NEC Electronics or others.

- Descriptions of circuits, software and other related information in this document are provided for illustrative purposes in semiconductor product operation and application examples. The incorporation of these circuits, software and information in the design of a customer's equipment shall be done under the full responsibility of the customer. NEC Electronics assumes no responsibility for any losses incurred by customers or third parties arising from the use of these circuits, software and information.

- While NEC Electronics endeavors to enhance the quality, reliability and safety of NEC Electronics products, customers agree and acknowledge that the possibility of defects thereof cannot be eliminated entirely. To minimize risks of damage to property or injury (including death) to persons arising from defects in NEC Electronics products, customers must incorporate sufficient safety measures in their design, such as redundancy, fire-containment and anti-failure features.

- NEC Electronics products are classified into the following three quality grades: "Standard", "Special" and "Specific". The "Specific" quality grade applies only to NEC Electronics products developed based on a customer-designated "quality assurance program" for a specific application. The recommended applications of an NEC Electronics products depend on its quality grade, as indicated below. Customers must check the quality grade of each NEC Electronics product before using it in a particular application.

- "Standard": Computers, office equipment, communications equipment, test and measurement equipment, audio and visual equipment, home electronic appliances, machine tools, personal electronic equipment and industrial robots.

- "Special": Transportation equipment (automobiles, trains, ships, etc.), traffic control systems, anti-disaster systems, anti-crime systems, safety equipment and medical equipment (not specifically designed for life support).

- "Specific": Aircraft, aerospace equipment, submersible repeaters, nuclear reactor control systems, life support systems and medical equipment for life support, etc.

The quality grade of NEC Electronics products is "Standard" unless otherwise expressly specified in NEC Electronics data sheets or data books, etc. If customers wish to use NEC Electronics products in applications not intended by NEC Electronics, they must contact an NEC Electronics sales representative in advance to determine NEC Electronics' willingness to support a given application.

(Note)

- (1) "NEC Electronics" as used in this statement means NEC Electronics Corporation and also includes its majority-owned subsidiaries.

- (2) "NEC Electronics products" means any product developed or manufactured by or for NEC Electronics (as defined above).

# **Regional Information**

Some information contained in this document may vary from country to country. Before using any NEC Electronics product in your application, please contact the NEC Electronics office in your country to obtain a list of authorized representatives and distributors. They will verify:

- · Device availability

- Ordering information

- · Product release schedule

- · Availability of related technical literature

- Development environment specifications (for example, specifications for third-party tools and components, host computers, power plugs, AC supply voltages, and so forth)

- Network requirements

In addition, trademarks, registered trademarks, export restrictions, and other legal issues may also vary from country to country.

#### [GLOBAL SUPPORT] http://www.necel.com/en/support/support.html

| NEC Electronics America, Inc. (U.S.)<br>Santa Clara, California<br>Tel: 408-588-6000<br>800-366-9782 | NEC Electronics (Europe) GmbH<br>Duesseldorf, Germany<br>Tel: 0211-65 03 01 | NEC Electronics Hong Kong Ltd.<br>Hong Kong<br>Tel: 2886-9318 |

|------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|---------------------------------------------------------------|

|                                                                                                      | Sucursal en España                                                          | NEC Electronics Hong Kong Ltd.                                |

|                                                                                                      | Madrid, Spain                                                               | Seoul Branch                                                  |

|                                                                                                      | Tel: 091-504 27 87                                                          | Seoul, Korea                                                  |

|                                                                                                      |                                                                             | Tel: 02-558-3737                                              |

|                                                                                                      | <ul> <li>Succursale Française</li> </ul>                                    |                                                               |

|                                                                                                      | Vélizy-Villacoublay, France                                                 | NEC Electronics Shanghai, Ltd.                                |

|                                                                                                      | Tel: 01-30-67 58 00                                                         | Shanghai, P.R. China                                          |

|                                                                                                      |                                                                             | Tel: 021-6841-1138                                            |

|                                                                                                      | <ul> <li>Filiale Italiana</li> </ul>                                        |                                                               |

Milano, Italy

Tel: 02-66 75 41

Tel: 040-244 58 45

• Tyskland Filial Taeby, Sweden

• Branch The Netherlands Eindhoven, The Netherlands NEC Electronics Taiwan Ltd. Taipei, Taiwan Tel: 02-2719-2377

NEC Electronics Singapore Pte. Ltd. Novena Square, Singapore Tel: 6253-8311

- Tel: 08-63 80 820 • United Kingdom Branch

- Milton Keynes, UK Tel: 01908-691-133

J03.4

# Major Revisions in This Edition (1/4)

| Page                       | Description                                                                                                                                      |

|----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| Throughout                 | <ul> <li>Addition of the following product.<br/>μPD703111GM-15-UEU</li> <li>Change of the following register name.<br/>PFCAL → PFCALL</li> </ul> |

| p.29                       | Addition of execution time of 150 MHz products to minimum instruction execution time in 1.2 Features                                             |

| p.45                       | Addition of Note in 2.1 (2) Non-port pins                                                                                                        |

| p.48                       | Addition of description in 2.3 (1) (b) (vii) UCLK (USB clock)                                                                                    |

| p.50                       | Modification of description in 2.3 (3) (b) (ii) DMAAK0, DMAAK1 (DMA acknowledge)                                                                 |

| p.52                       | Modification of description in 2.3 (5) (b) (ii) DMAAK2, DMAAK3 (DMA acknowledge)                                                                 |

| p.68                       | Addition of execution time of 150 MHz products to minimum instruction execution time in 3.1 Features                                             |

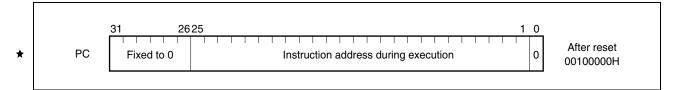

| p.70                       | Modification of default value in 3.2.1 (2) Program counter (PC)                                                                                  |

| pp.86, 98                  | Modification of description in 3.4.7 Peripheral I/O registers                                                                                    |

| p.111                      | Change of table of VSWC setting values in 3.4.9 System wait control register (VSWC)                                                              |

| p.115                      | Modification of description in 4.2.1 Pin status during internal instruction RAM, internal data RAM, and peripheral I/O access                    |

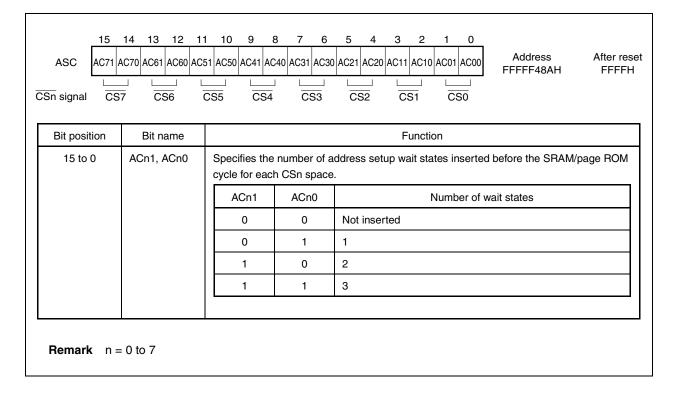

| p.121                      | Modification of description when BTn1 and BTn0 bits are set to 11 in 4.4.1 (1) Bus cycle type configuration registers 0, 1 (BCT0, BCT1)          |

| p.122                      | Modification of table of number of access clocks in 4.5.1 Number of access clocks                                                                |

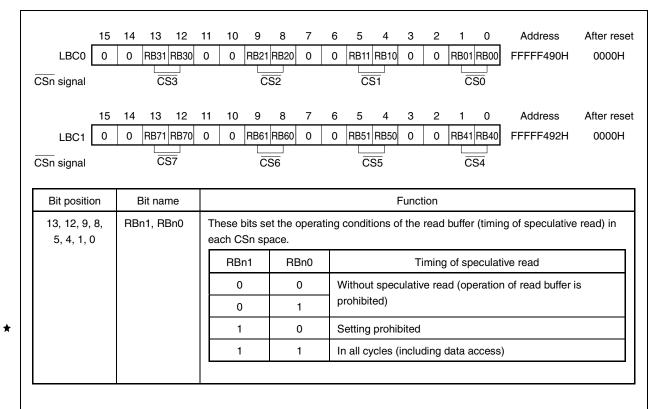

| p.146                      | Addition to <b>Cautions</b> and modification of description in <b>4.5.6 (1) Line buffer control registers 0, 1 (LBC0, LBC1)</b>                  |

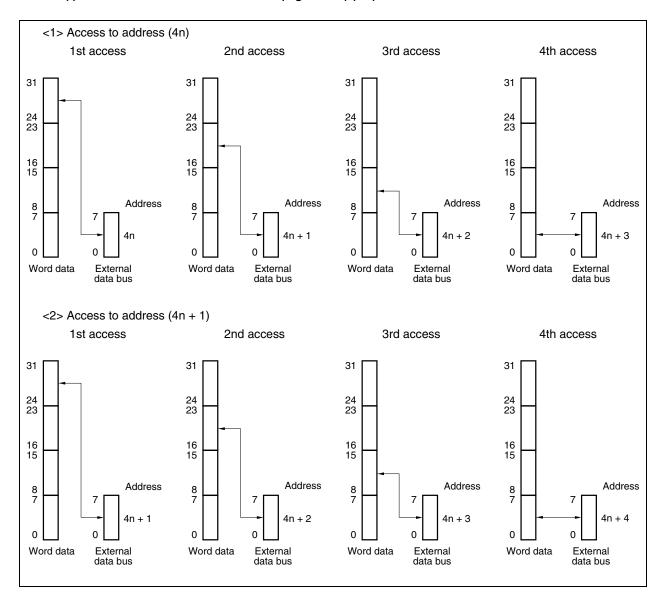

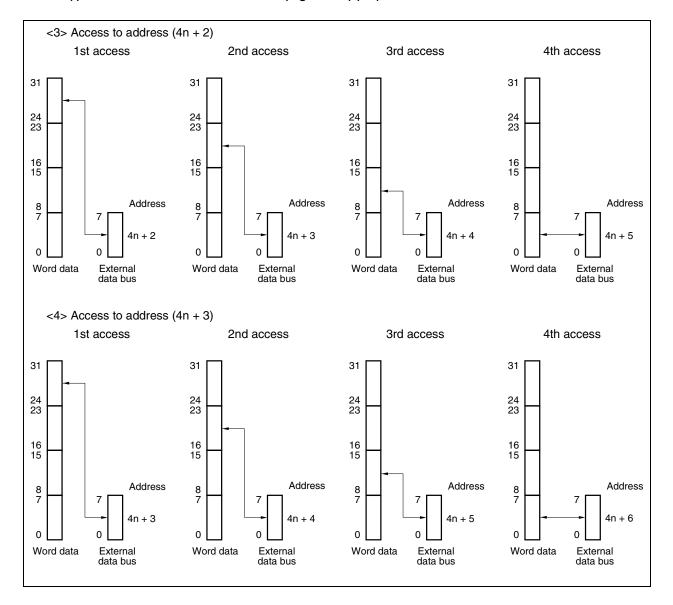

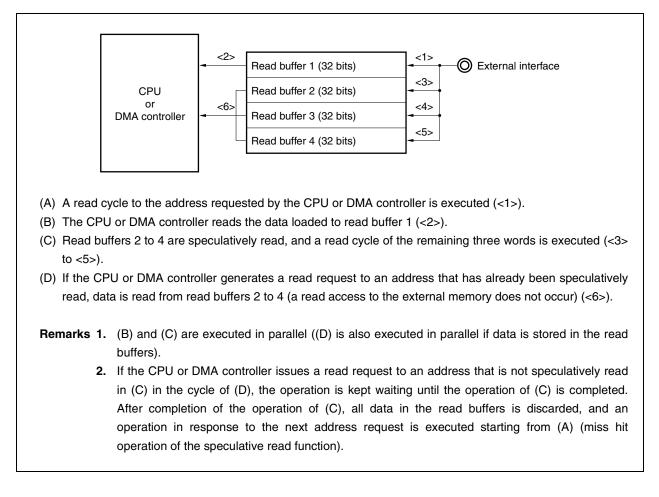

| p.147                      | Addition of Remark in 4.5.6 (1) (a) Speculative read function (read buffer function)                                                             |

| pp.148, 149                | Modification of description, addition of Note, and addition to Cautions in 4.5.6 (1) (b) Write buffer function                                   |

| p.155                      | Addition to Cautions in 4.7.1 (3) Bus cycle period control register (BCP)                                                                        |

| p.161                      | Modification of Cautions in 4.9.1 (1) Cache configuration register (BHC)                                                                         |

| p.170                      | Addition of (5) in 4.10.3 Cautions                                                                                                               |

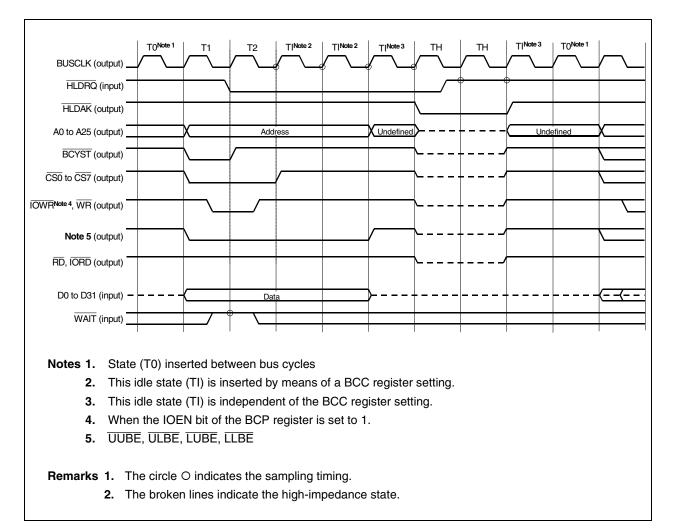

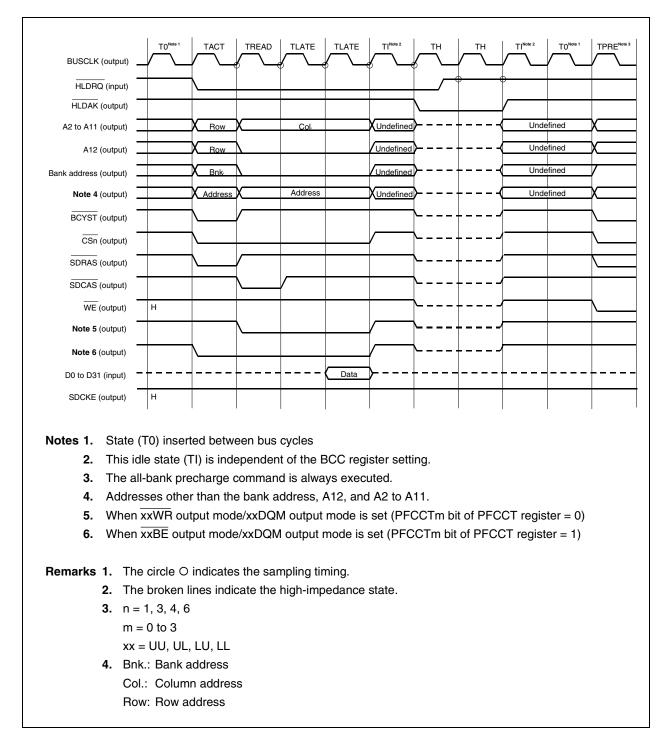

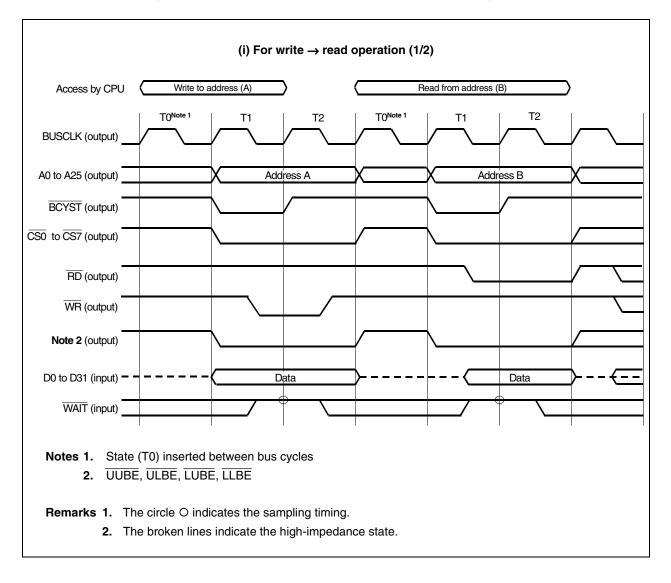

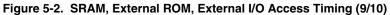

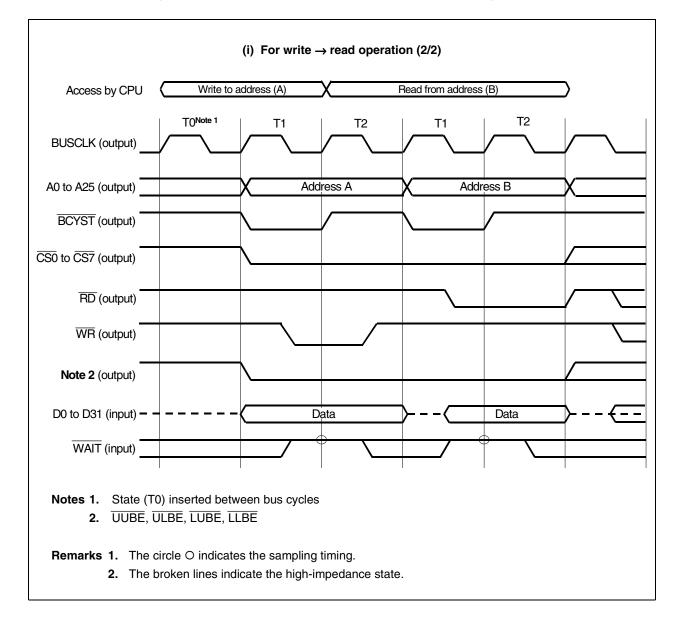

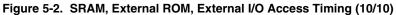

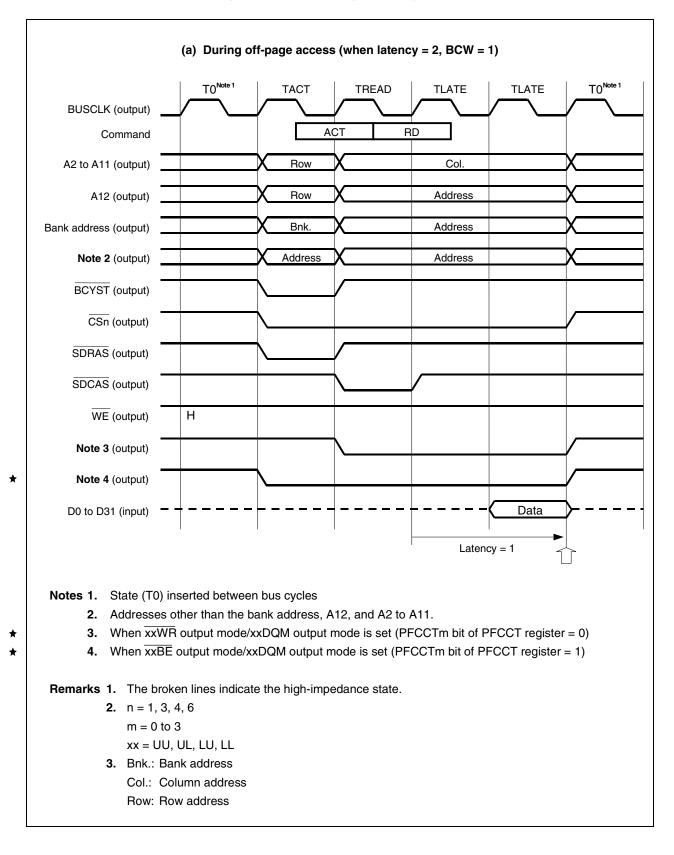

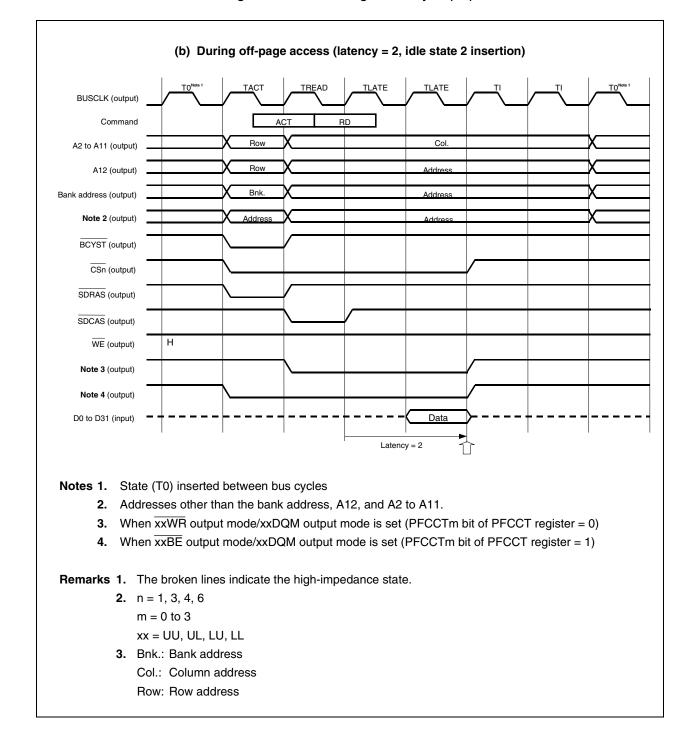

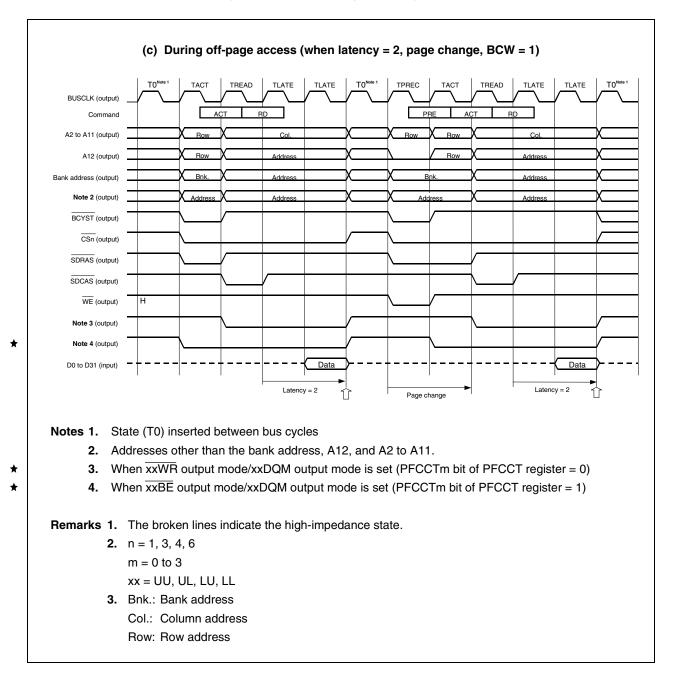

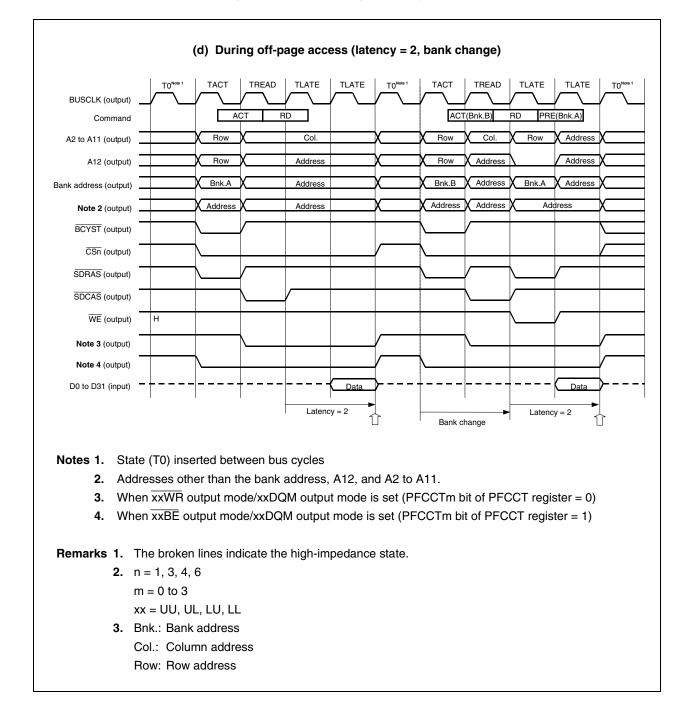

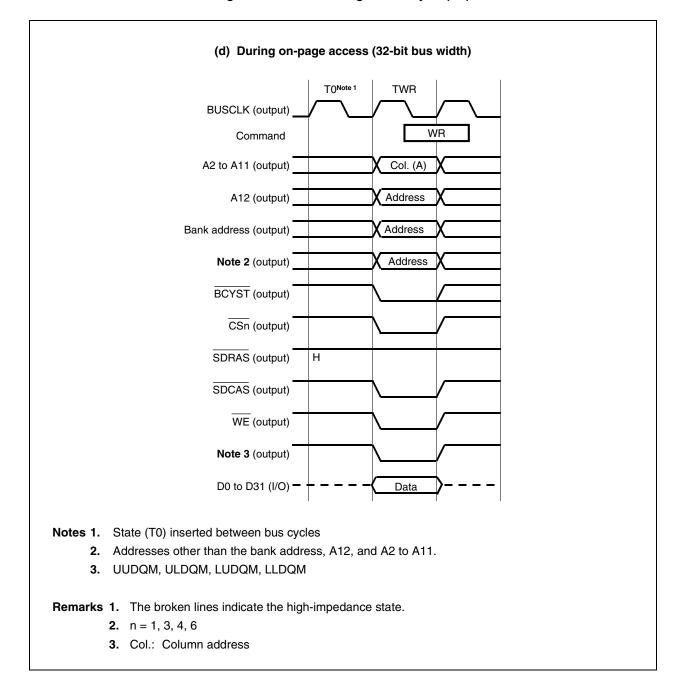

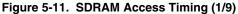

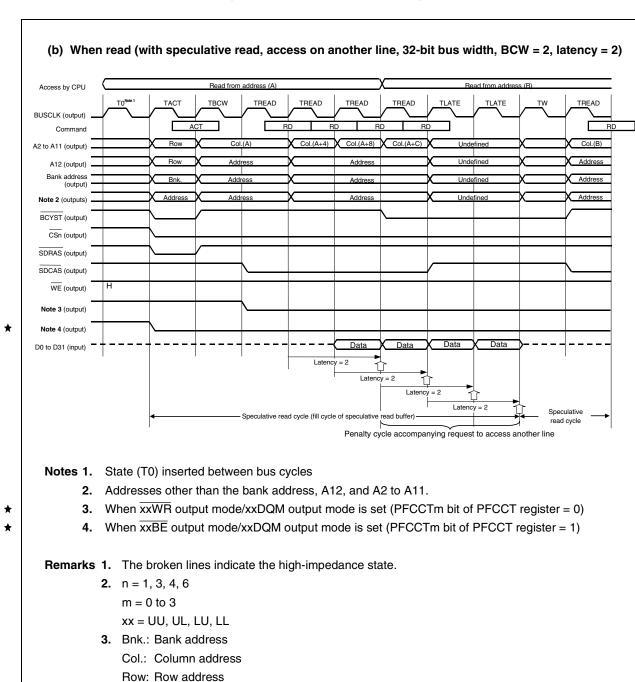

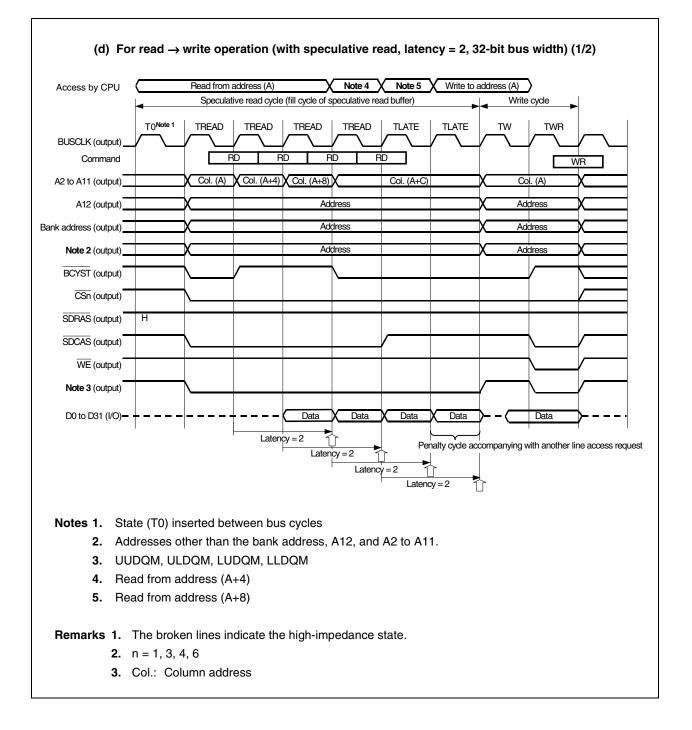

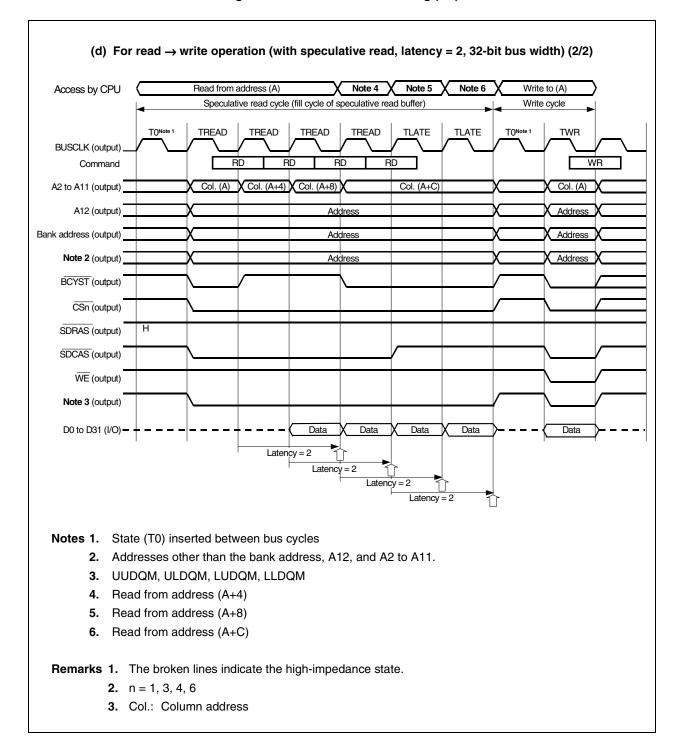

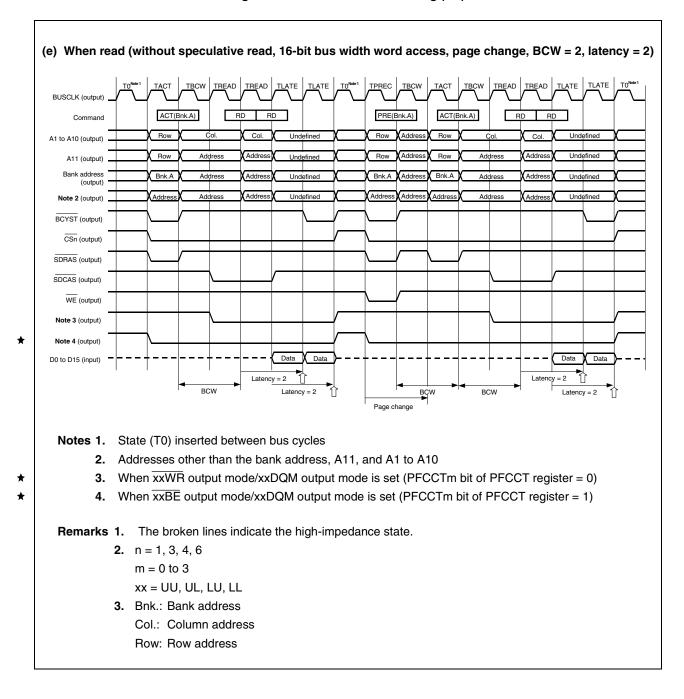

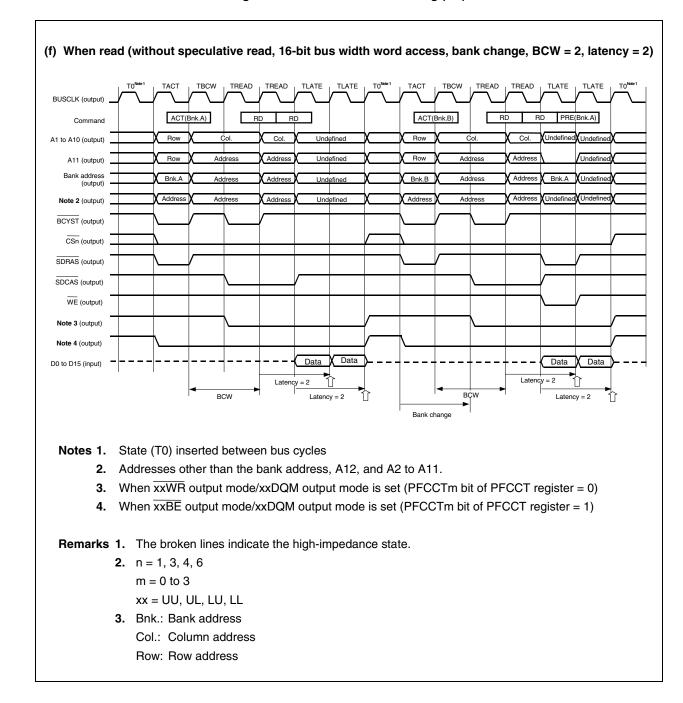

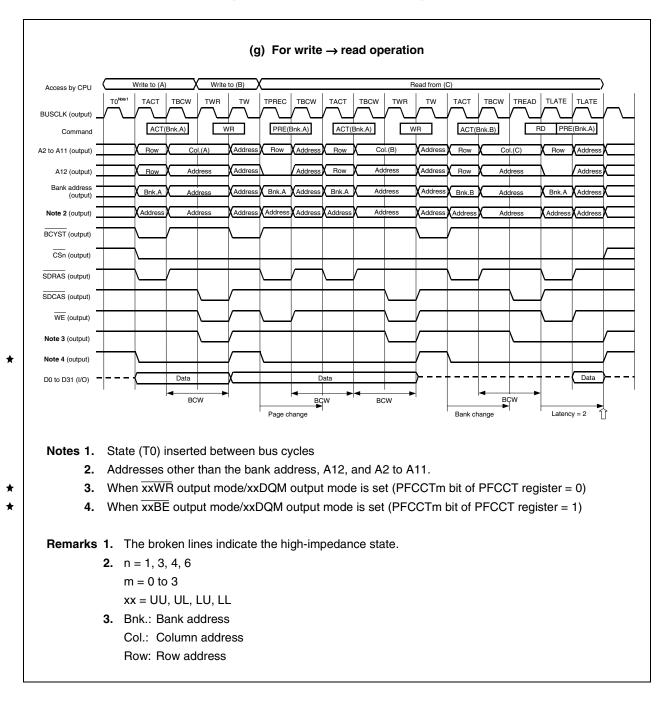

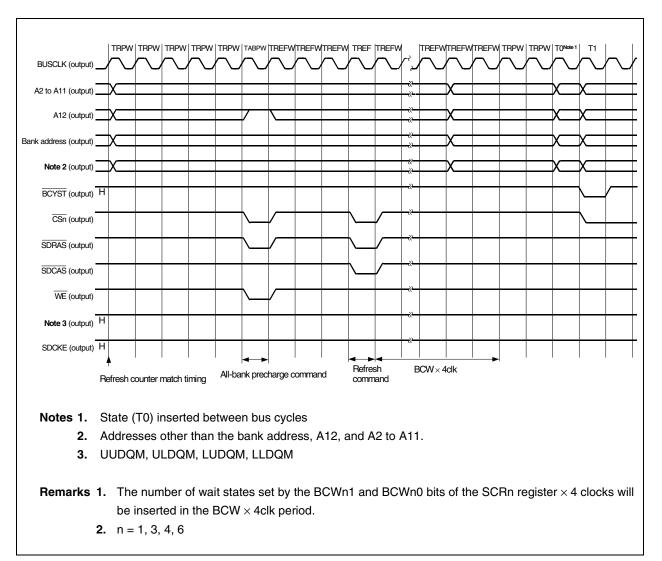

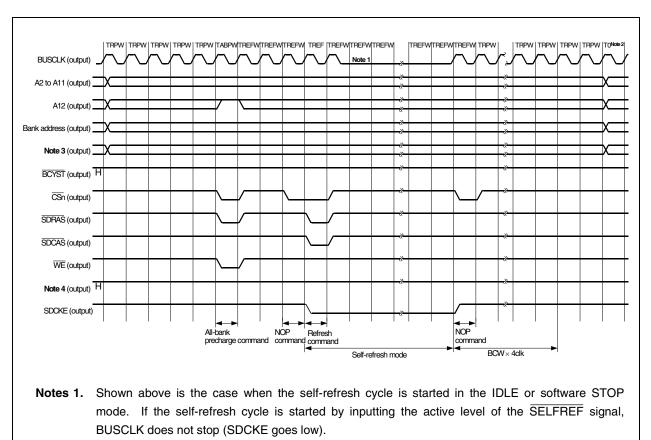

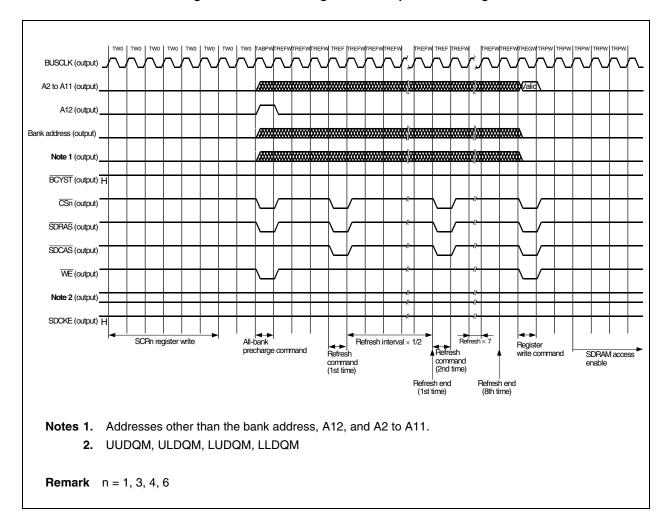

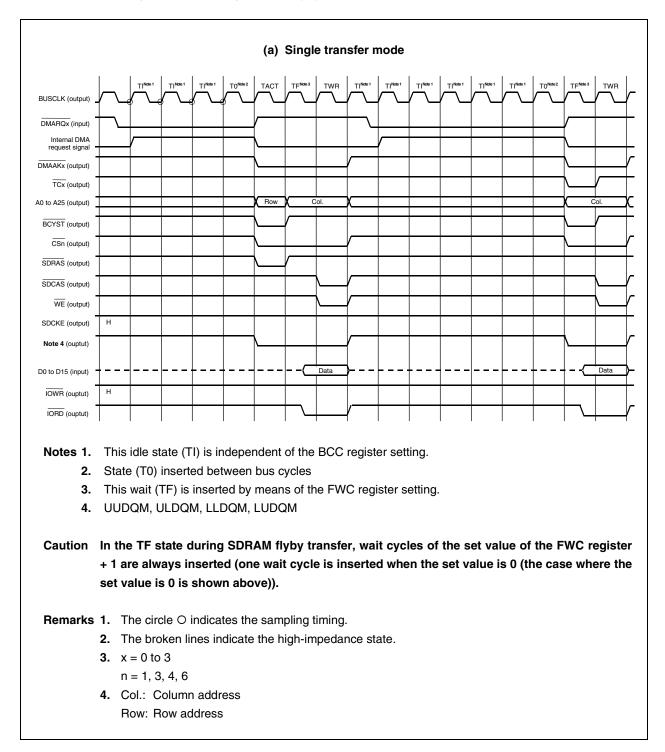

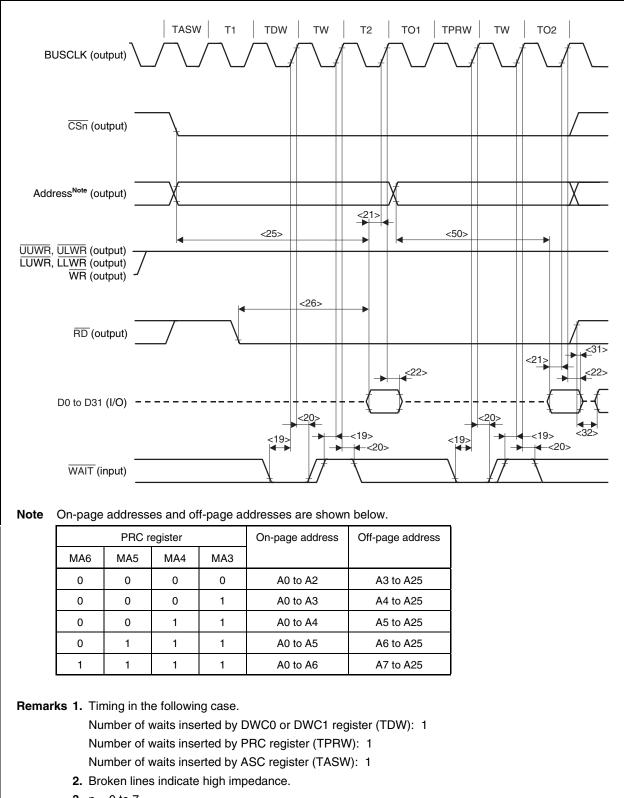

| p.177                      | Addition of timing and modification of Notes in 4.11.6 (1) SDRAM (when read, latency = 2, no idle state insertion)                               |

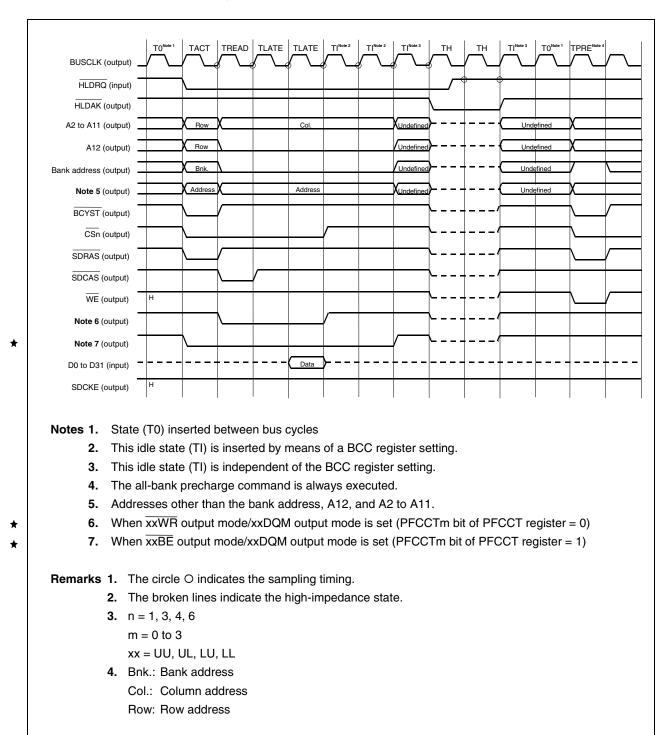

| p.178                      | Addition of timing and modification of Notes in 4.11.6 (2) SDRAM (when read, latency = 2, two idle states inserted, 32-bit bus width)            |

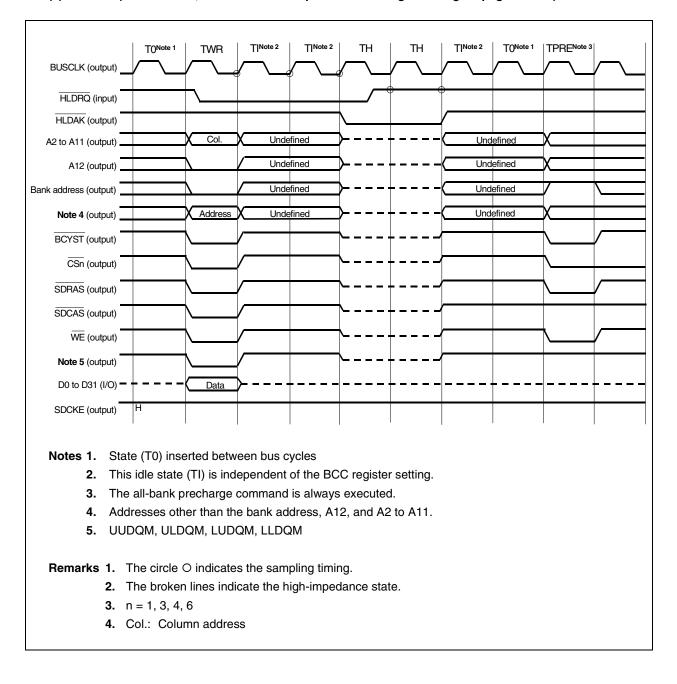

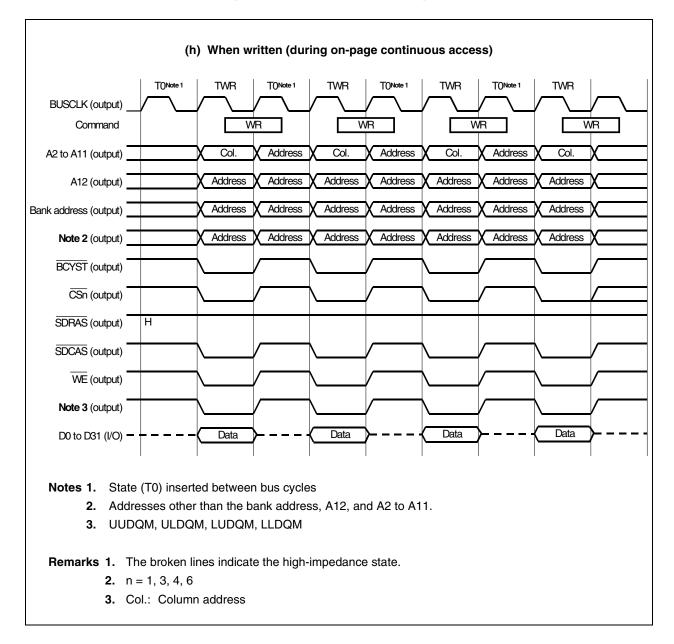

| p.179                      | Addition of timing and modification of Notes in 4.11.6 (3) SDRAM (when written)                                                                  |

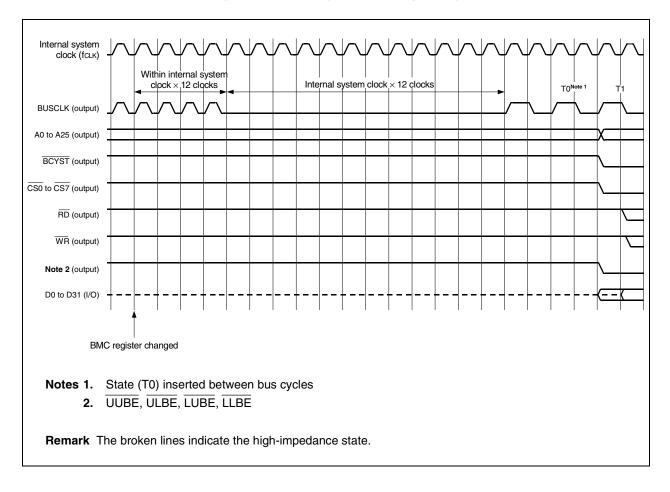

| p.182                      | Addition of 4.14 Timing at Which T0 State Is Not Inserted                                                                                        |

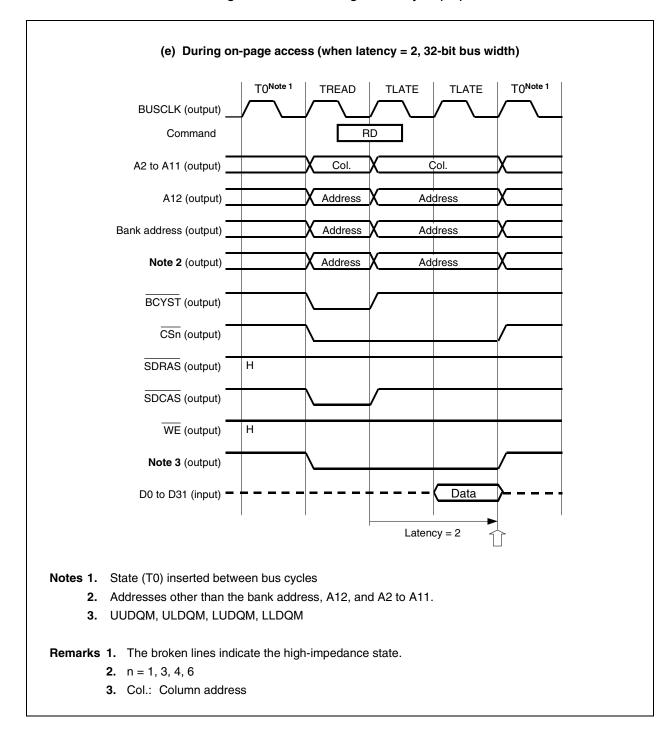

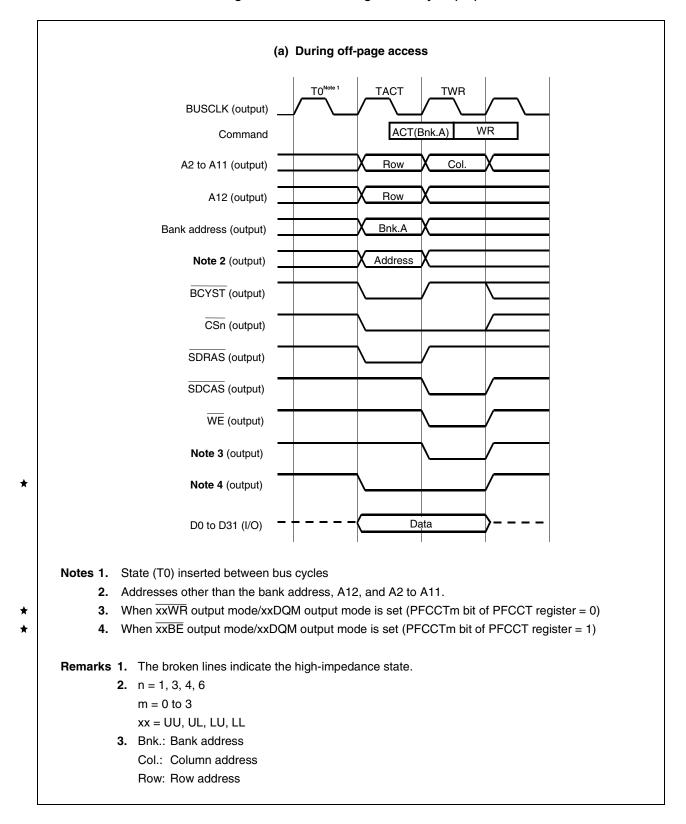

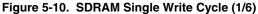

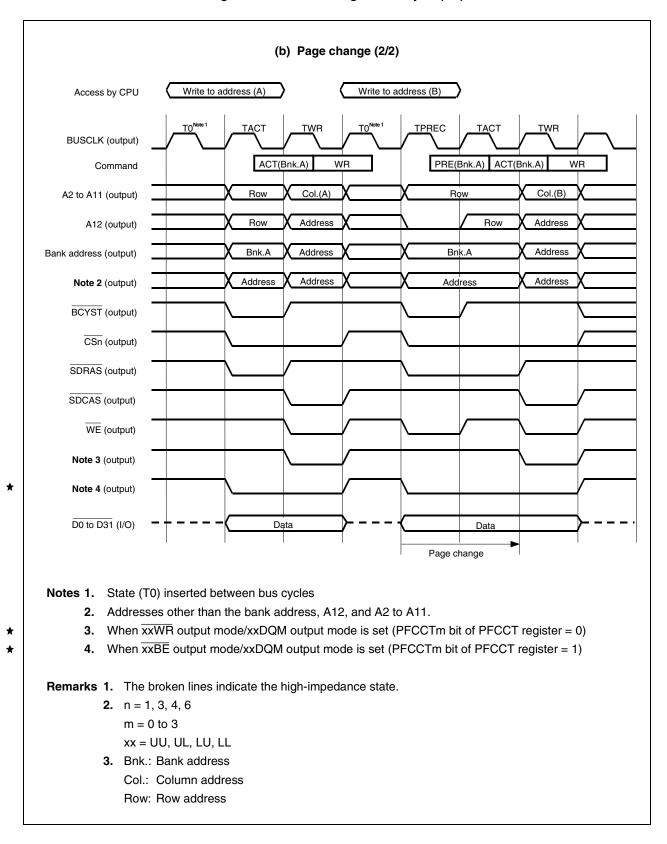

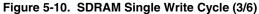

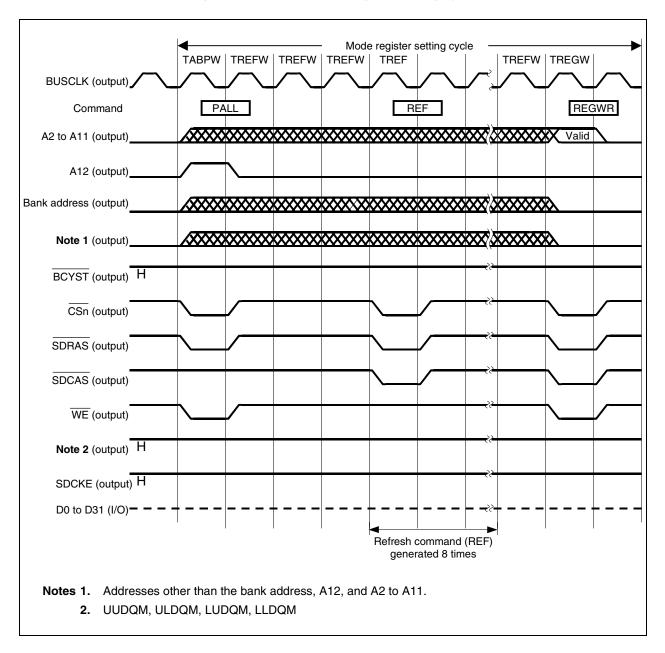

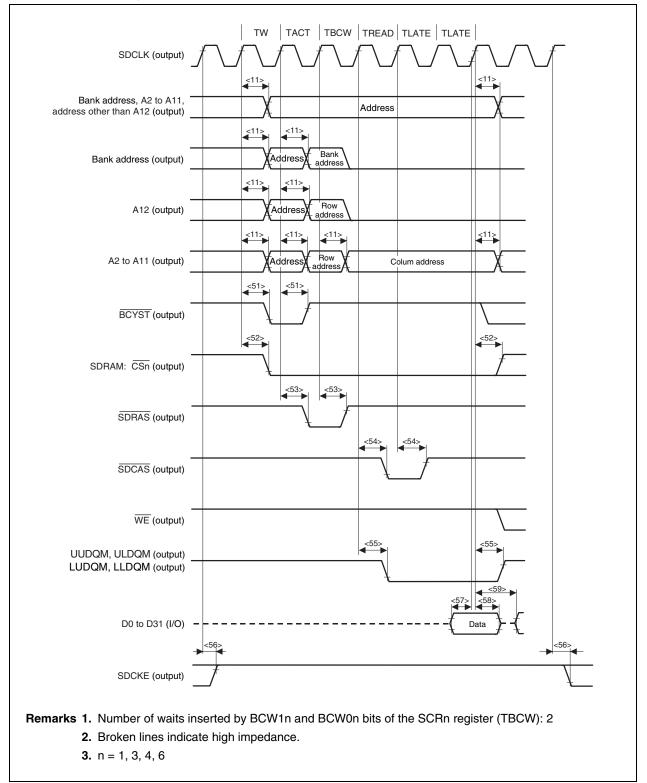

| pp.214 to 217              | Addition of timing and modification of Notes in Figure 5-9 SDRAM Single Read Cycle                                                               |

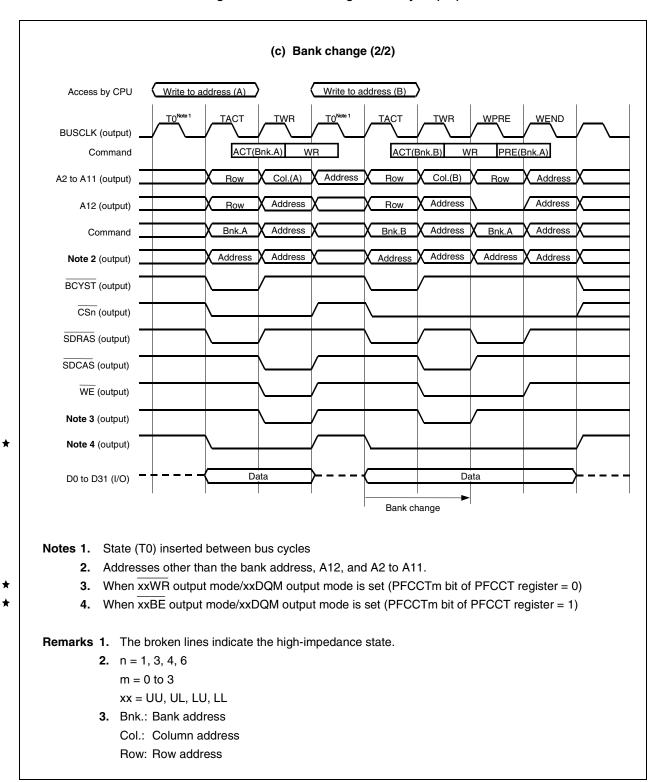

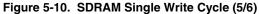

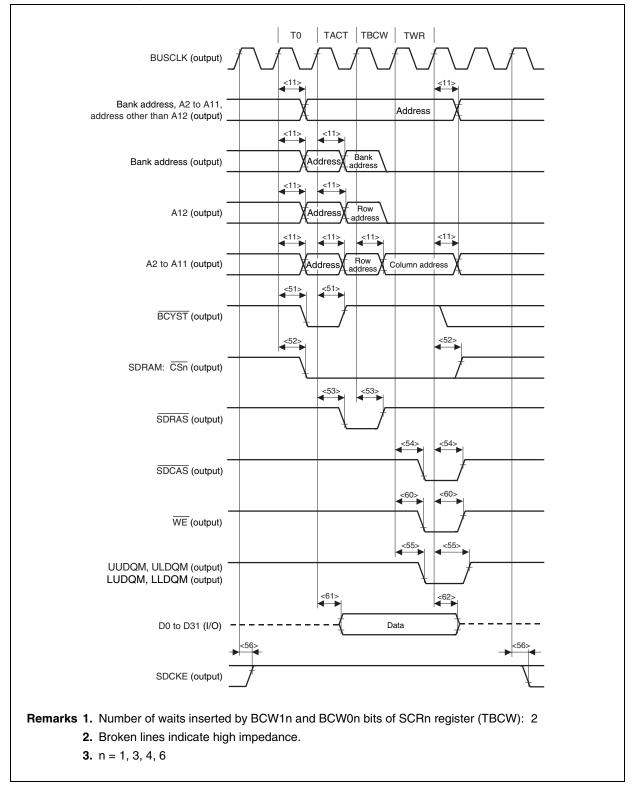

| pp.220 to 224              | Addition of timing and modification of Notes in Figure 5-10 SDRAM Single Write Cycle                                                             |

| pp.227, 228,<br>232 to 234 | Addition of timing and modification of Notes in Figure 5-11 SDRAM Access Timing                                                                  |

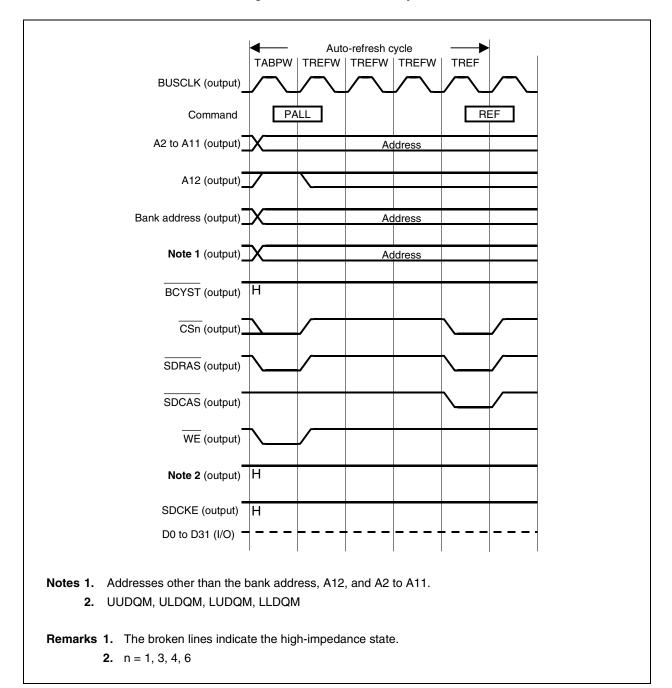

| p.236                      | Modification of Caution in 5.3.6 (1) SDRAM refresh control registers 1, 3, 4, 6 (RFS1, RFS3, RFS4, RFS6)                                         |

| p.238                      | Modification of description in Table 5-1 Example of Interval Factor Settings                                                                     |

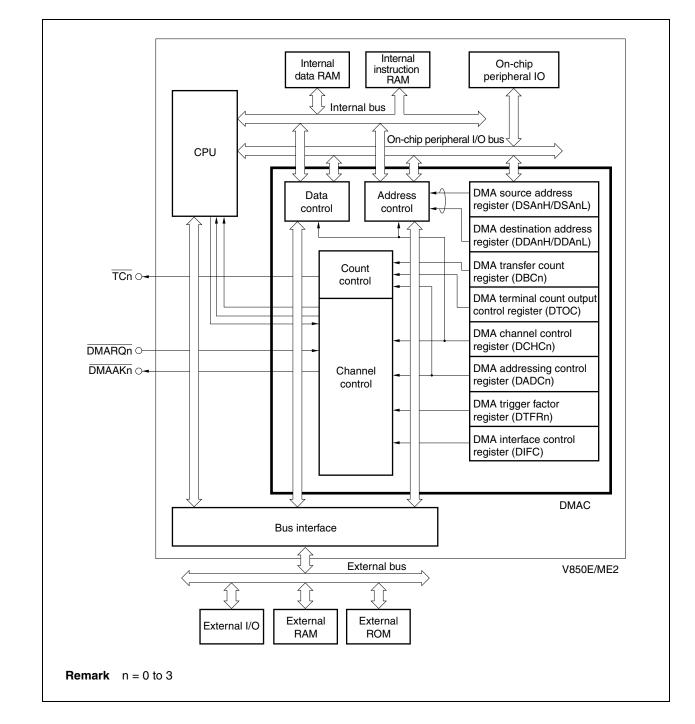

| p.247                      | Addition of internal instruction RAM in block diagram in 6.2 Configuration                                                                       |

| p.248                      | Addition to Cautions in 6.3.1 (1) DMA source address registers 0H to 3H (DSA0H to DSA3H)                                                         |

| p.250                      | Addition to Cautions in 6.3.2 (1) DMA destination address registers 0H to 3H (DDA0H to DDA3H)                                                    |

# Major Revisions in This Edition (2/4)

| Page          | Description                                                                                                                                    |

|---------------|------------------------------------------------------------------------------------------------------------------------------------------------|

| p.252         | Addition to Cautions in 6.3.3 DMA transfer count registers 0 to 3 (DBC0 to DBC3)                                                               |

| p.253         | Addition to Cautions in 6.3.4 DMA addressing control registers 0 to 3 (DADC0 to DADC3)                                                         |

| pp.256, 257   | Addition to Cautions and description in 6.3.5 DMA channel control registers 0 to 3 (DCHC0 to DCHC3)                                            |

| p.259         | Addition to Cautions and description in 6.3.6 DMA terminal count output control register (DTOC)                                                |

| p.260         | Addition to Cautions in 6.3.7 DMA trigger factor registers 0 to 3 (DTFR0 to DTFR3)                                                             |

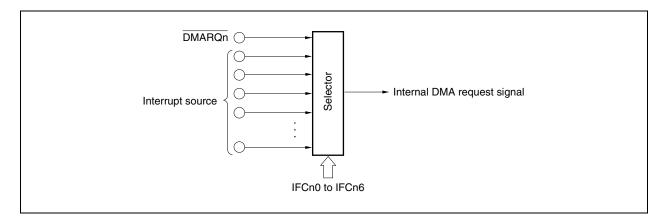

| pp.264, 265   | Addition of 6.3.7 (1) DMA request detection function                                                                                           |

| p.266         | Addition of <b>Caution</b> and <b>Note</b> and modification of description in <b>6.3.8 DMA interface control register</b> (DIFC)               |

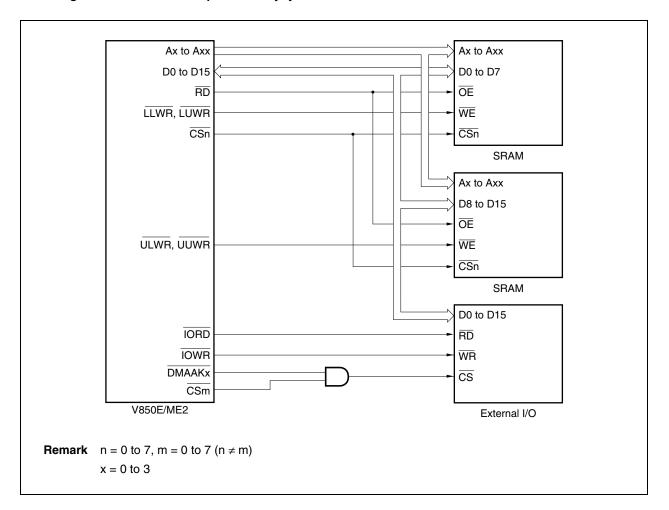

| p.276         | Addition of timing and modification of Notes in Figure 6-12 Timing of 2-Cycle DMA Transfer (SDRAM $\rightarrow$ SRAM)                          |

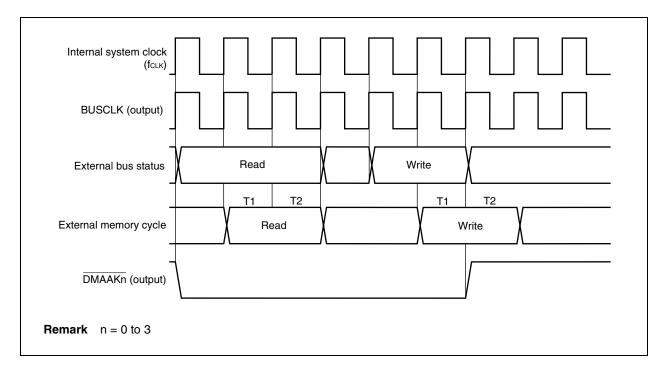

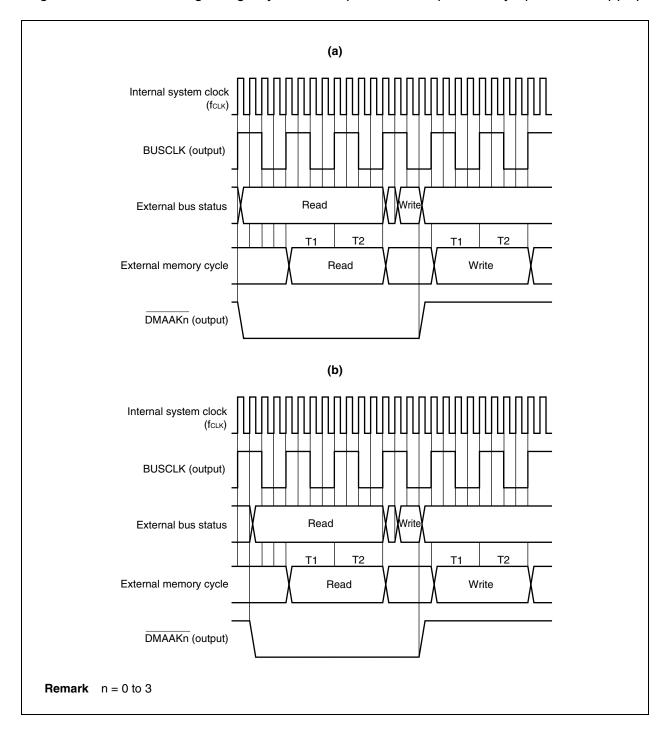

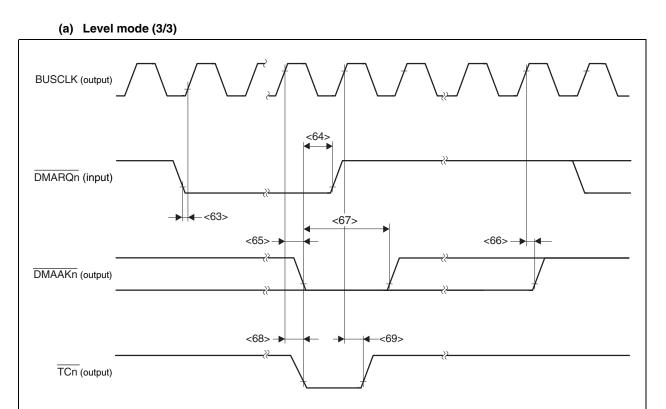

| p.278         | Addition of 6.5.1 (1) Timing of DMARQn and DMAAKn signals for 2-cycle transfer                                                                 |

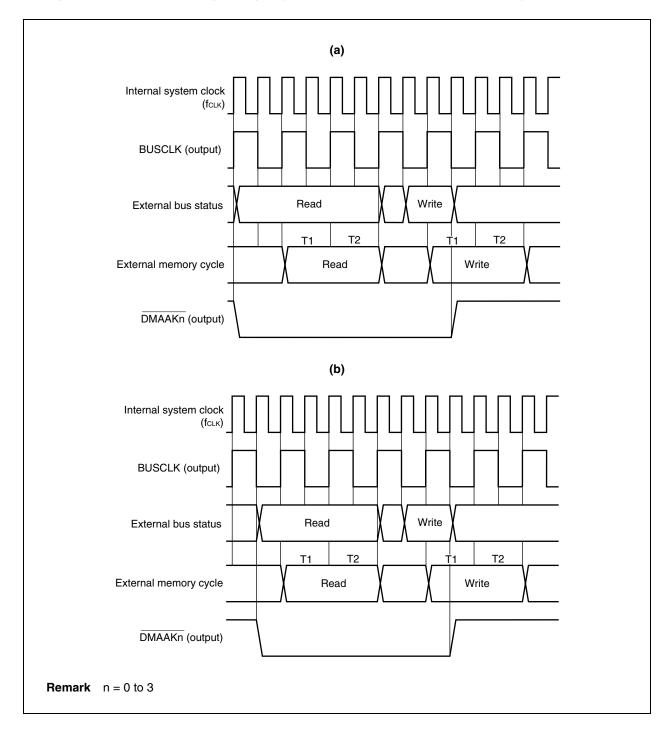

| p.280         | Addition of 6.5.1 (2) DMAAKn signal active width extension function                                                                            |

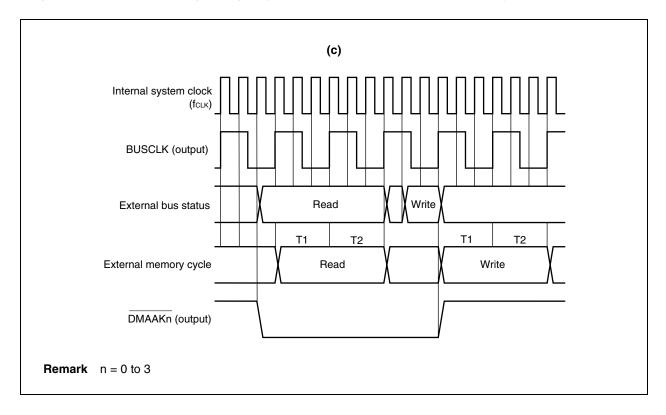

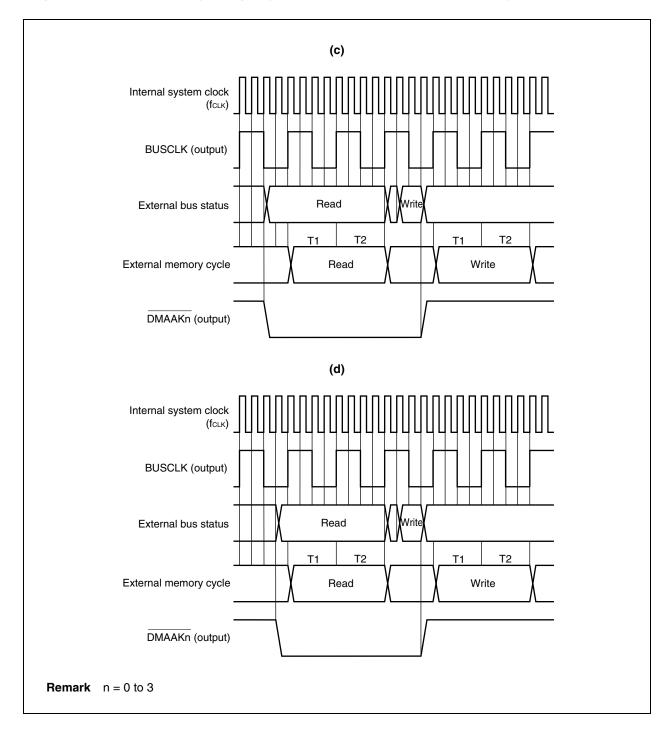

| p.282         | Addition of 6.5.1 (3) Outline of 2-cycle transfer timing                                                                                       |

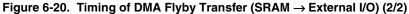

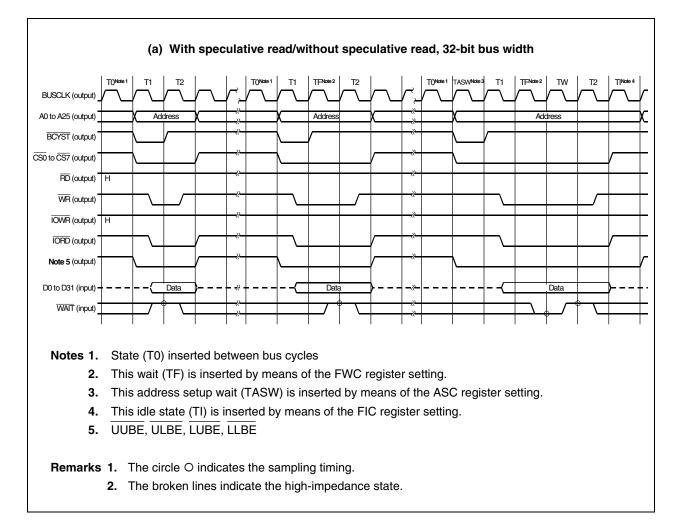

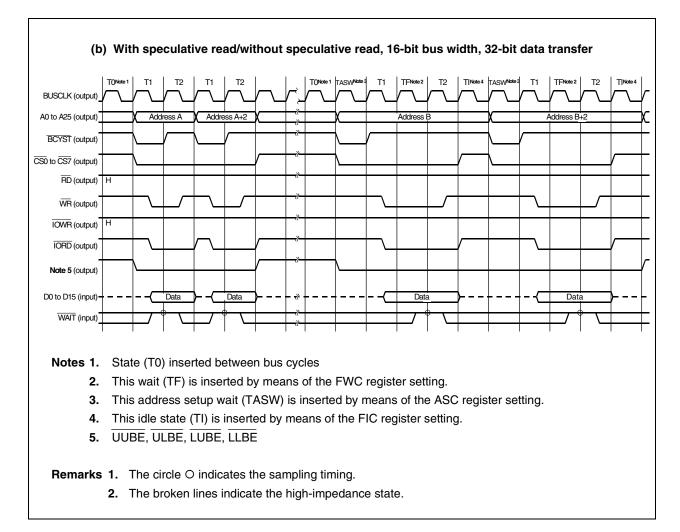

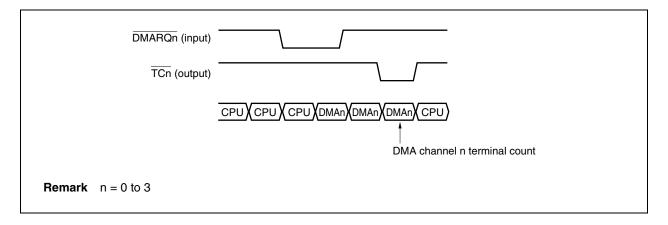

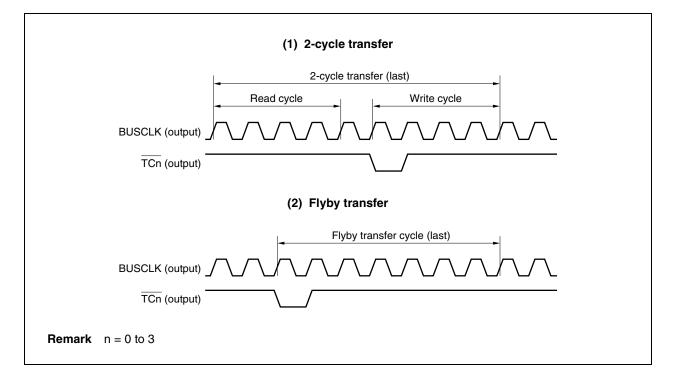

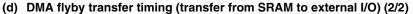

| pp.289 to 291 | Modification of timing in Figure 6-19 Timing of DMA Flyby Transfer (External I/O $\rightarrow$ SDRAM)                                          |

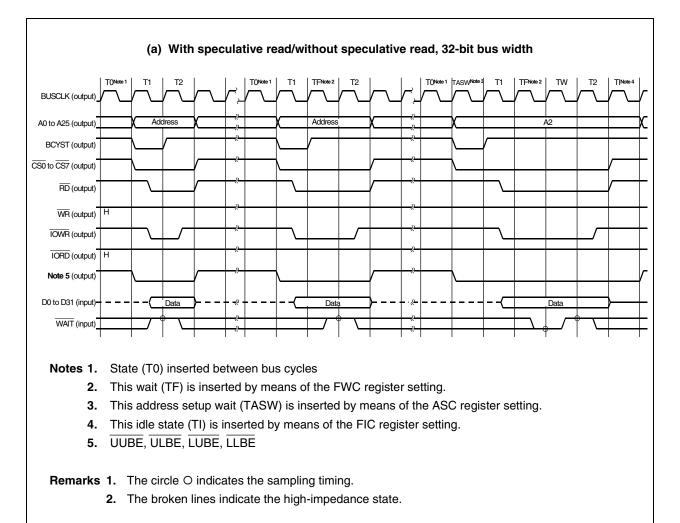

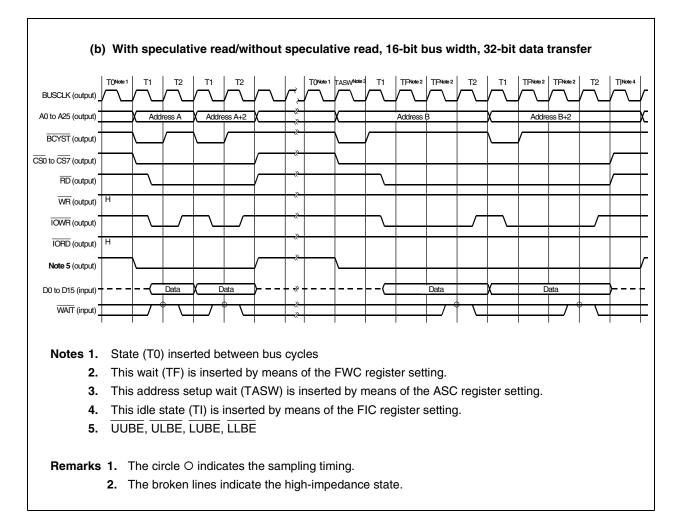

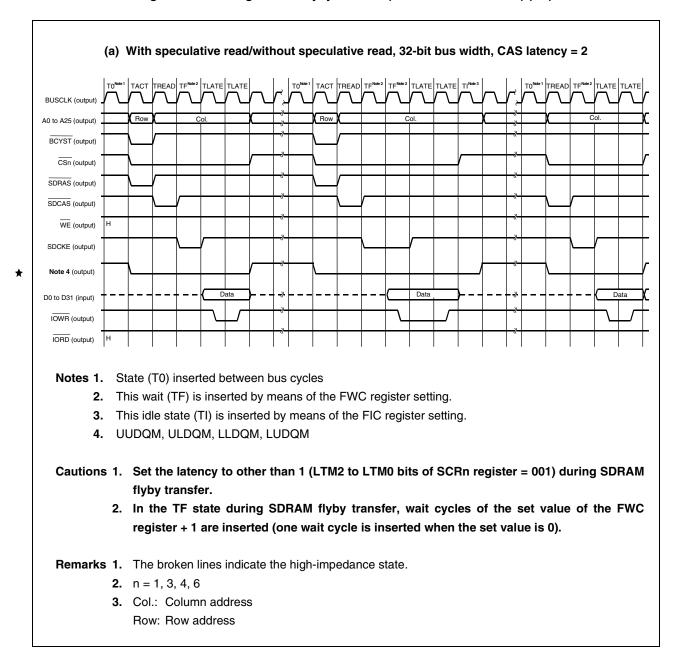

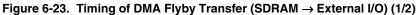

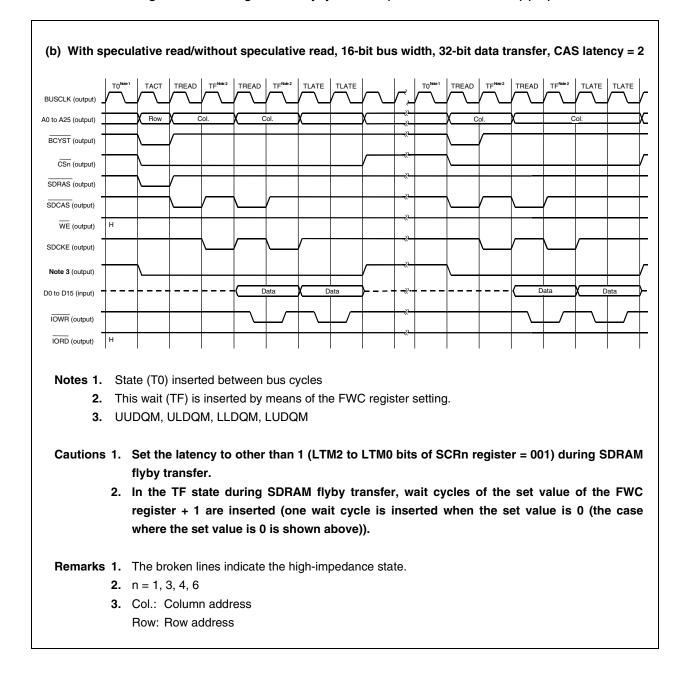

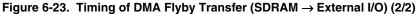

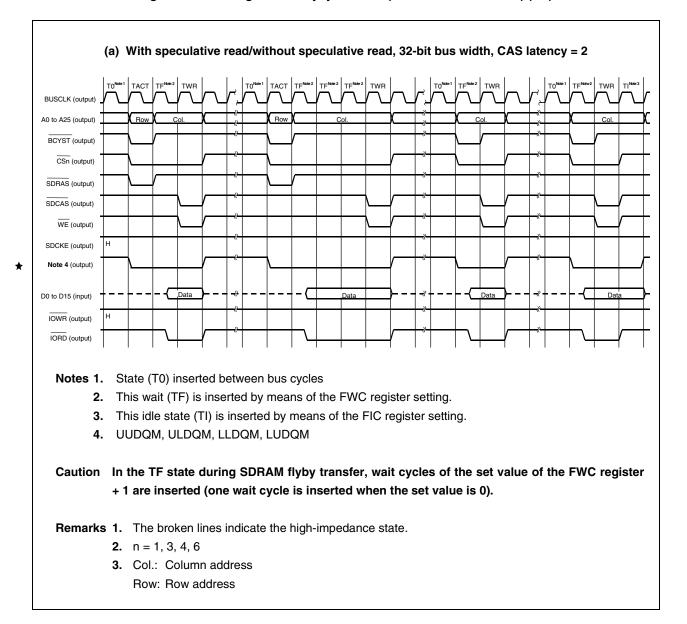

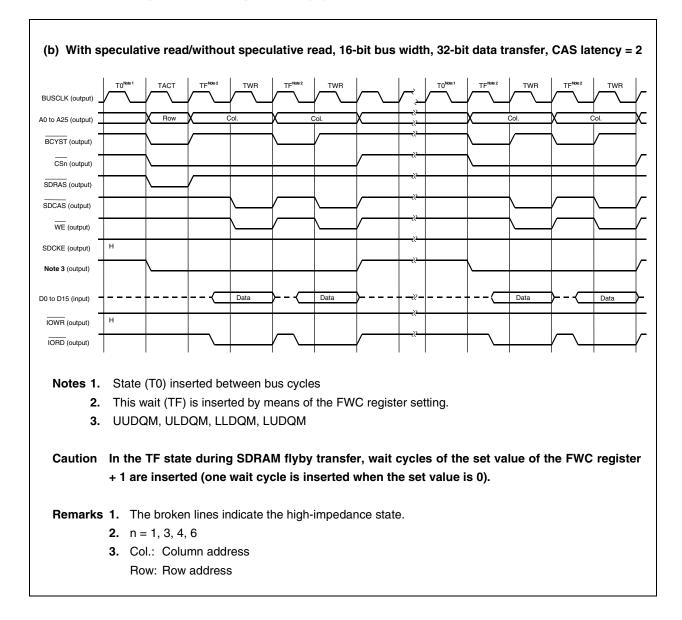

| pp.298, 299   | Modification of timing in Figure 6-23 Timing of DMA Flyby Transfer (SDRAM → External I/O)                                                      |

| pp.300, 301   | Modification of timing in Figure 6-24 Timing of DMA Flyby Transfer (External I/O $\rightarrow$ SDRAM)                                          |

| p.302         | Modification of description and addition to Caution in Table 6-5 Relationship Between Transfer Type and Transfer Object                        |

| p.305         | Addition of description in 6.8 Next Address Setting Function                                                                                   |

| p.307         | Addition of Cautions in 6.9 DMA Transfer Start Factors                                                                                         |

| p.312         | Modification of description in 6.13 Times Related to DMA Transfer                                                                              |

| p.314         | Modification of description in 6.15 (3) Bus arbitration for CPU                                                                                |

| p.315         | Addition of 6.15 (7) Read values of DSAn and DDAn registers                                                                                    |

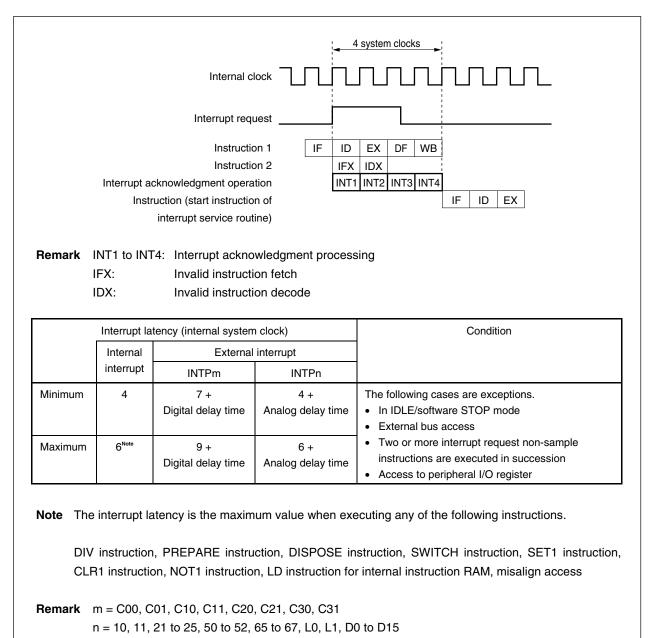

| p.363         | Modification of Note in Figure 7-14 Pipeline Operation at Interrupt Request Acknowledgment (Outline)                                           |

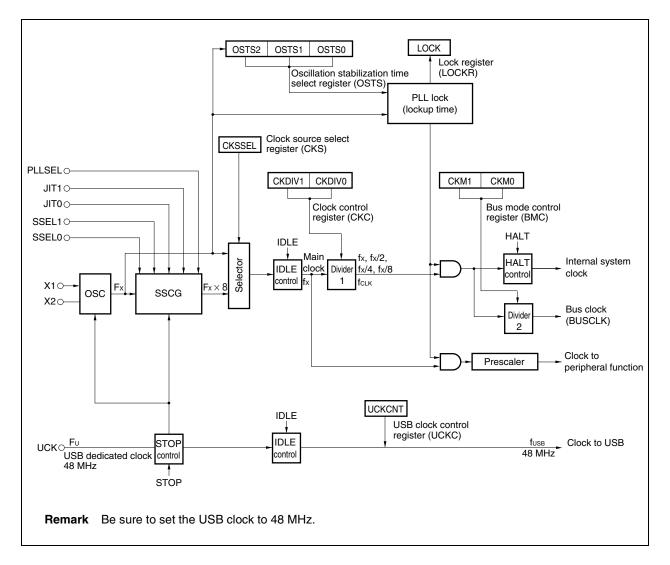

| p.365         | Modification of selection of SSCG output by PLLSEL pin and MDL-Selector Table (modulation period) in 8.1 Features                              |

| pp.367, 368   | Addition to Cautions and modification of description in 8.3.1 Clock control register (CKC)                                                     |

| p.370         | Modification of sample coding <2> for data setting sequence of clock source select register (CKS) in 8.3.2 Clock source select register (CKS)  |

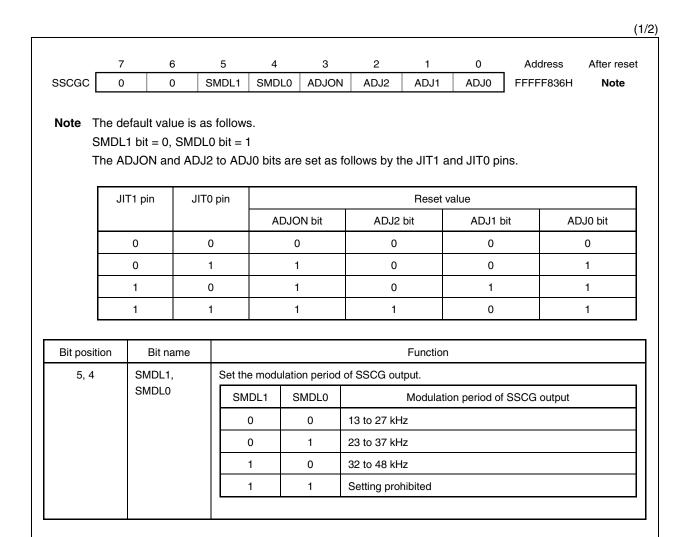

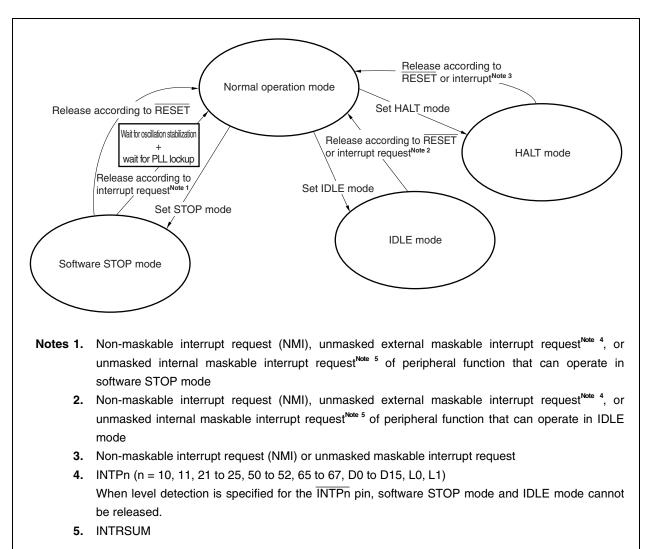

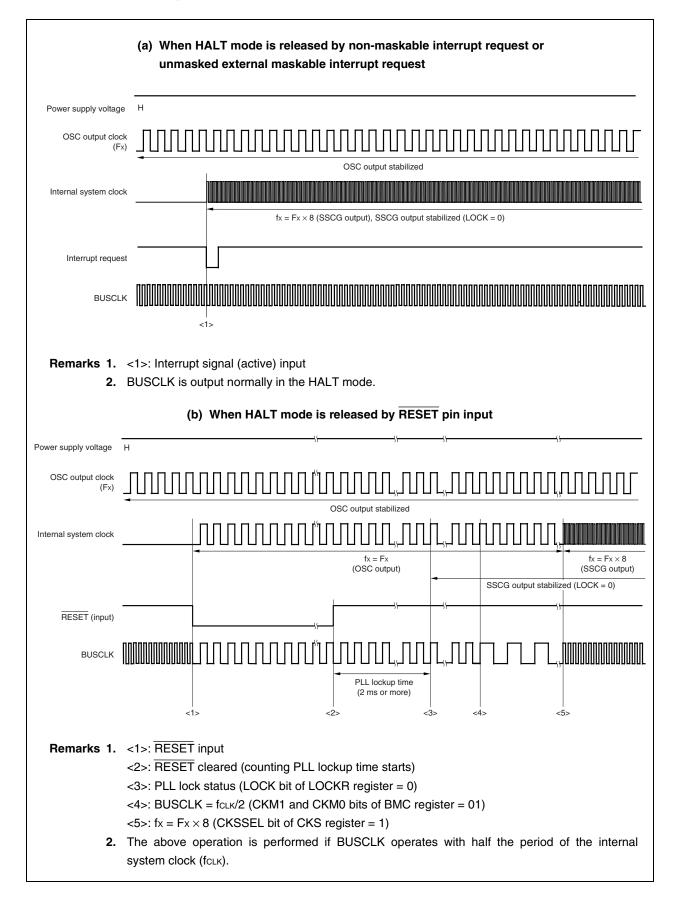

| pp.371, 372   | Modification of description in 8.3.3 SSCG control register (SSCGC)                                                                             |

| p.373         | Addition of Caution in 8.3.4 USB clock control register (UCKC)                                                                                 |

| p.375         | Modification of oscillation stabilization time in 8.3.6 Oscillation stabilization time select register (OSTS)                                  |

| p.376         | Addition to Notes in Table 8-1 Operation Status of Each Clock                                                                                  |

| p.376         | Modification of description in Table 8-2 Frequency List                                                                                        |

| p.377         | Addition of 8.5 Operating Clock Provisions                                                                                                     |

| p.400         | Modification of oscillation stabilization time in Table 8-11 Counting Time Examples                                                            |

| p.412         | Addition to Caution in 9.1.5 (2) Timer mode control registers C01 to C51 (TMCC01 to TMCC51)                                                    |

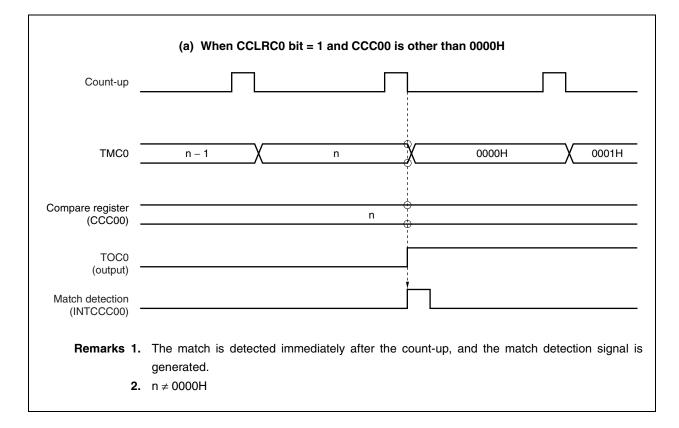

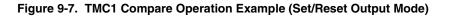

| p.422         | Modification of Figure 9-7 TMC1 Compare Operation Example (Set/Reset Output Mode)                                                              |

| p.459         | Addition of noise elimination width when $fx = 150$ MHz in Table 9-6 Relationship Between NCW1n Register Set Value and Noise Elimination Width |

# Major Revisions in This Edition (3/4)

| Page          | Description                                                                                                                                                                               |

|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| p.475         | Addition of 9.3.7 (6) Overflow interrupt signal (INTOV1n) and underflow interrupt signal (INTUD1n)                                                                                        |

| p.477         | Modification of transfer rate in 10.2.1 Features                                                                                                                                          |

| p.479         | Modification of description in 10.2.2 (10) UARTBn receive data register AP (UBnRXAP), UARTBn receive data register (UBnRX) (n = 0, 1)                                                     |

| p.480         | Addition of description in 10.2.2 (12) UARTBn transmit data register n (UBnTX) (n = 0, 1)                                                                                                 |

| p.487         | Modification of Caution in 10.2.3 (3) UARTBn control register 2 (UBnCTL2) (n = 0, 1)                                                                                                      |

| p.488         | Addition of description in 10.2.3 (4) UARTBn transmit data register (UBnTX) (n = 0, 1)                                                                                                    |

| p.489         | Modification of description in 10.2.3 (5) UARTBn receive data register AP (UBnRXAP), UARTBn receive data register (UBnRX) (n = 0, 1)                                                      |

| pp.491, 492   | Addition and modification of description in 10.2.3 (6) UARTBn FIFO control register 0 (UBnFIC0) (n = 0, 1)                                                                                |

| p.493         | Modification of description in 10.2.3 (7) UARTBn FIFO control register 1 (UBnFIC1) (n = 0, 1)                                                                                             |

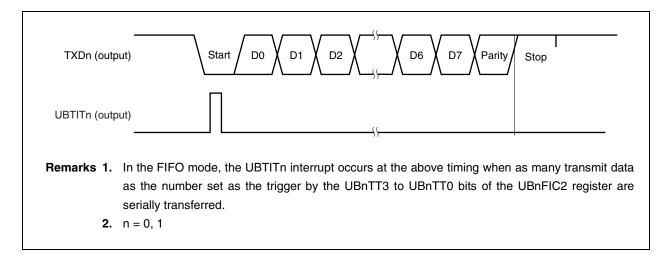

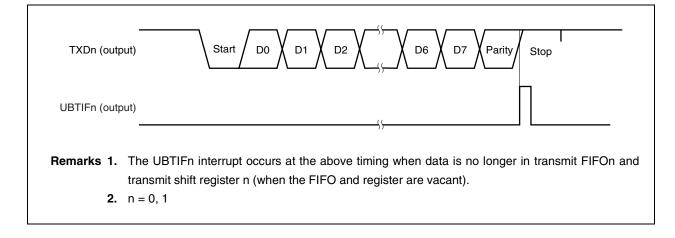

| p.501         | Addition of description in 10.2.4 (5) (b) FIFO mode                                                                                                                                       |

| p.503         | Addition of description in 10.2.5 (2) Pending mode/pointer mode                                                                                                                           |

| p.503         | Addition of Note in 10.2.5 (2) (a) (i) During transmission (writing to transmit FIFOn)                                                                                                    |

| p.504         | Addition of Note in 10.2.5 (2) (a) (ii) During reception (reading from receive FIFOn)                                                                                                     |

| p.512         | Addition of description in 10.2.6 (4) (c) (ii) Reception timeout interrupt (UBTITOn) (in FIFO mode only)                                                                                  |

| p.518         | Addition of value when fx = 150 MHz in Table 10-4 Baud Rate Generator Setting Data                                                                                                        |

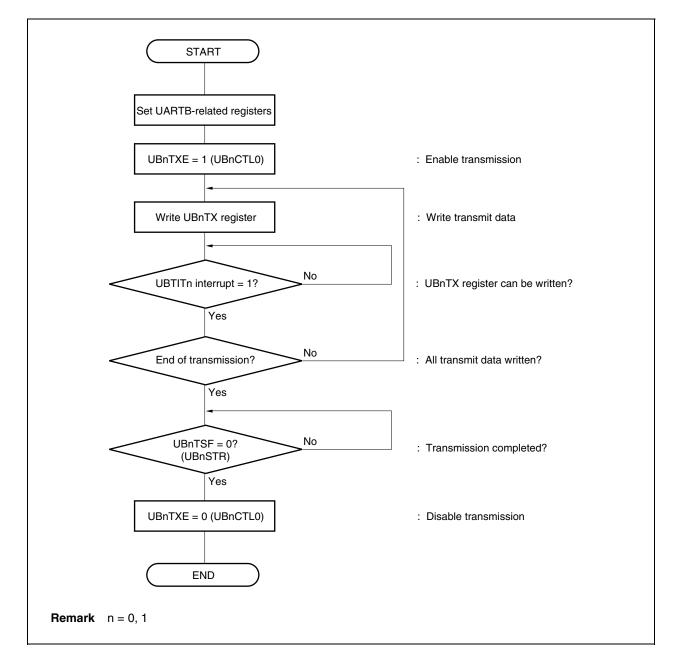

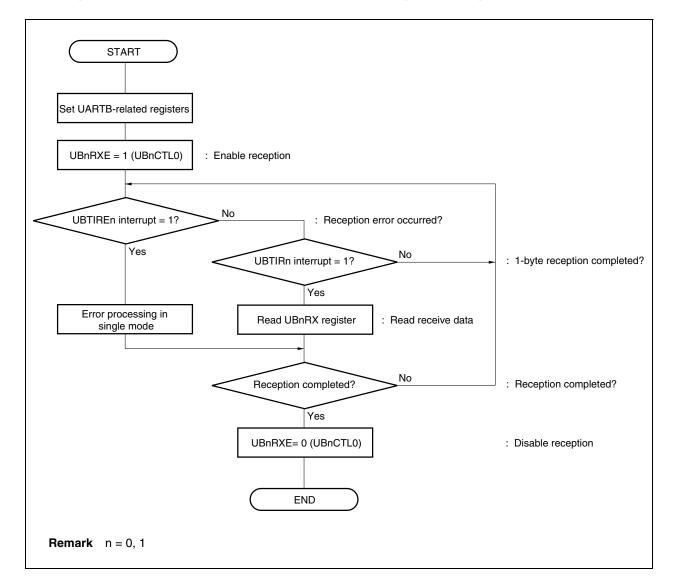

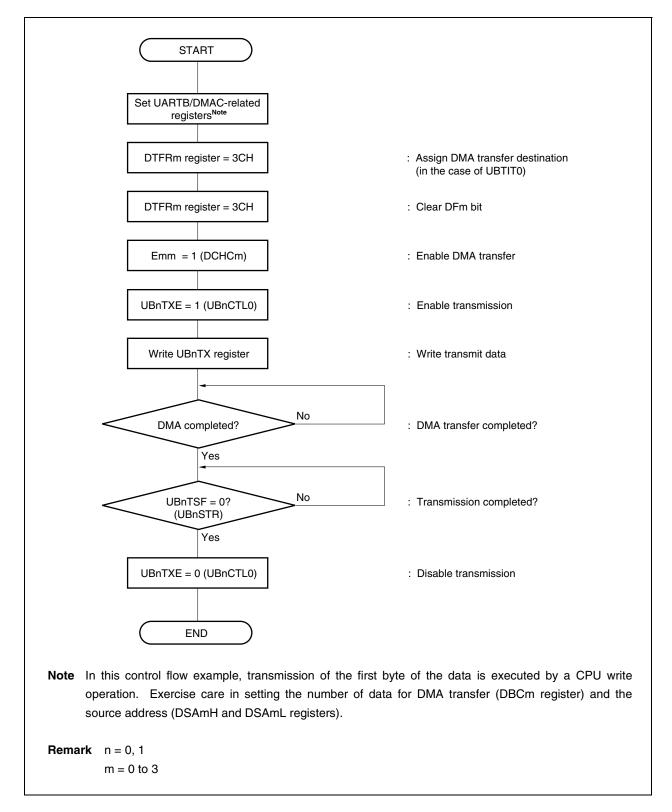

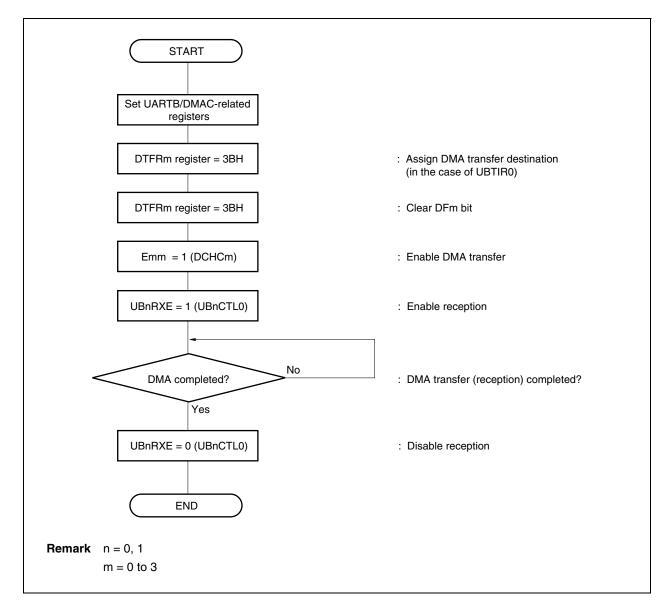

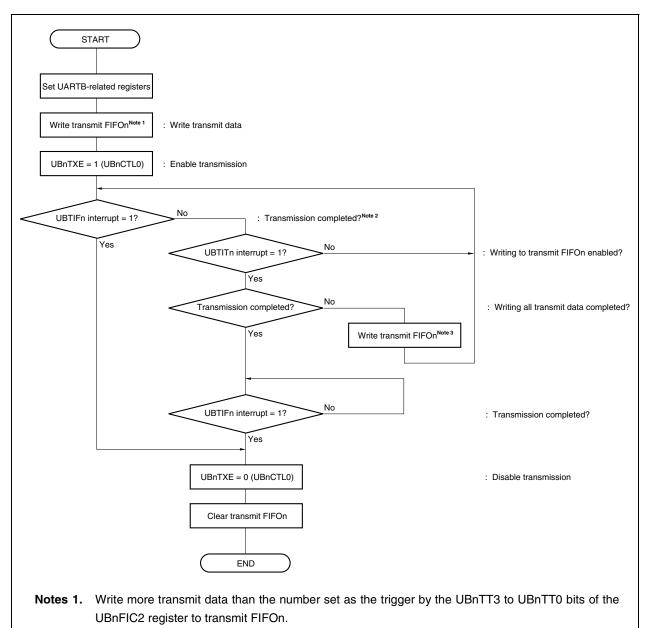

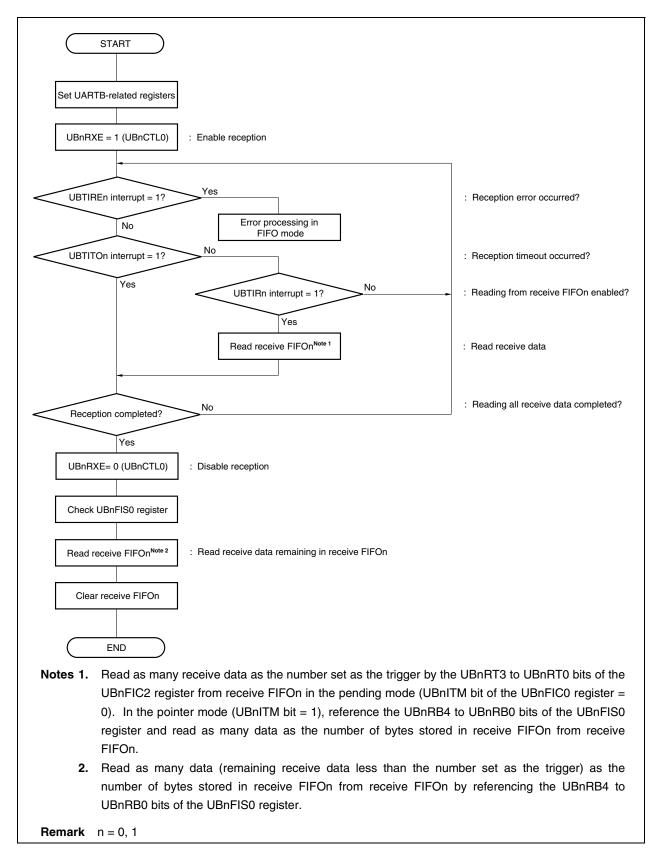

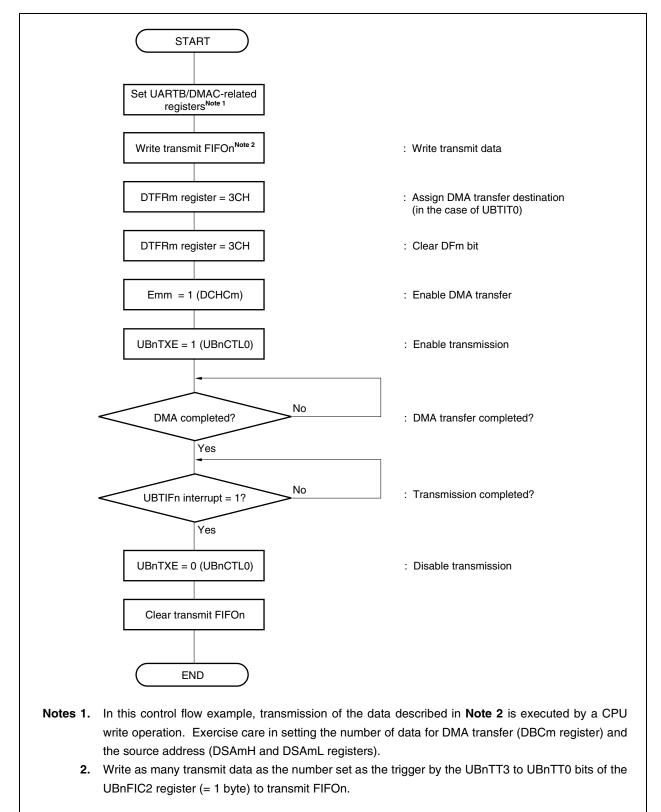

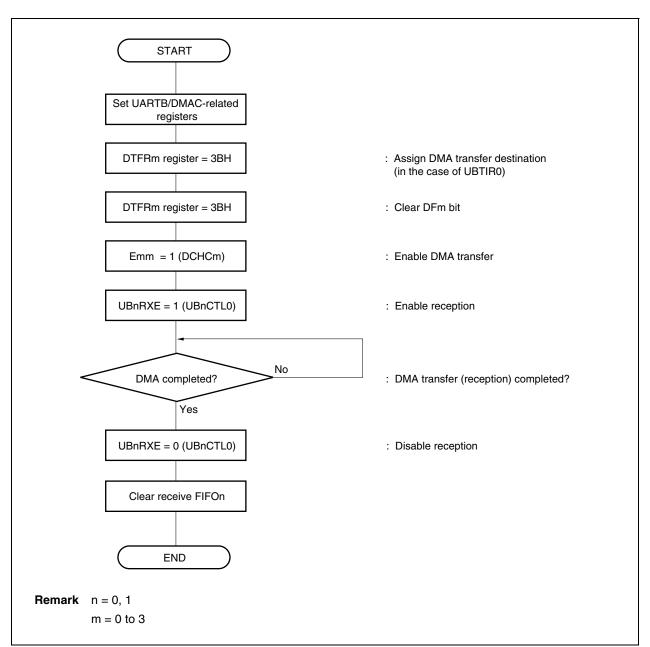

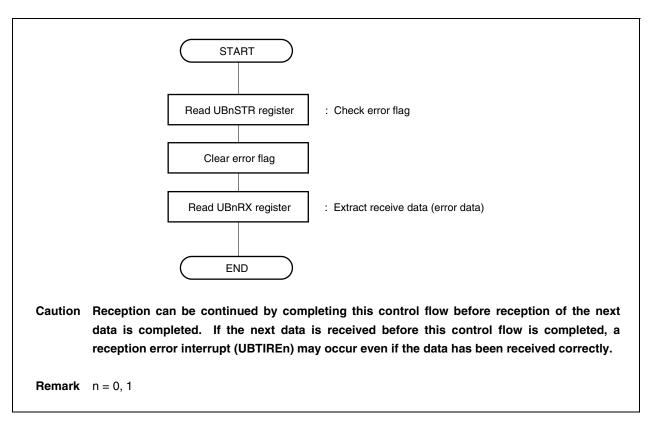

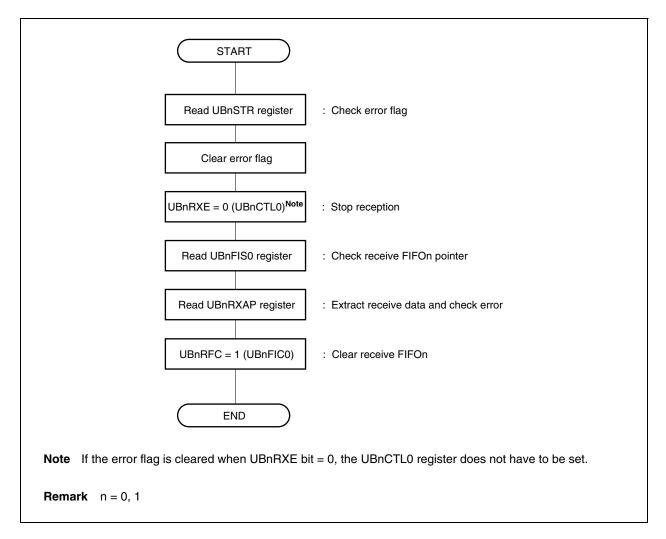

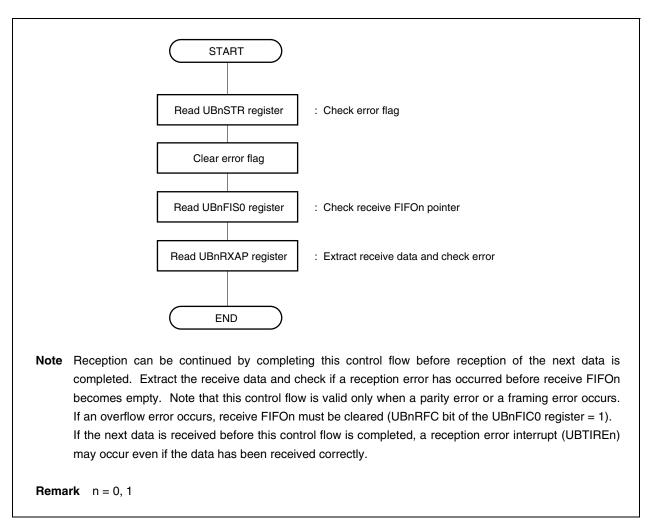

| p.522         | Addition of 10.2.8 Control flow                                                                                                                                                           |

| p.535         | Modification of description in Figure 10-22 Block Diagram of Clocked Serial Interfaces 30 and 31                                                                                          |

| p.536         | Modification of description of Caution 2 in 10.3.3 (1) Clocked serial interface mode registers 30, 31 (CSIM30, CSIM31)                                                                    |

| p.540         | Modification of description in 10.3.3 (2) Clocked serial interface clock select registers 30, 31 (CSIC30, CSIC31)                                                                         |

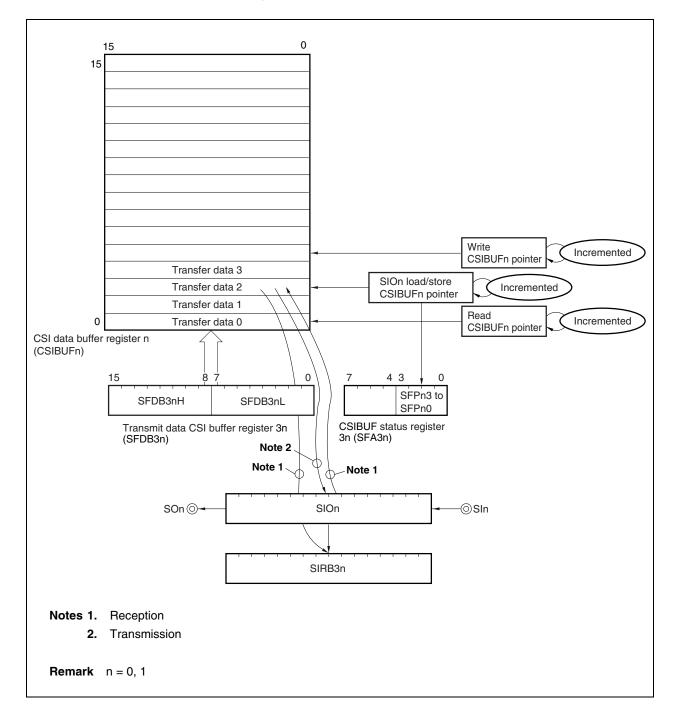

| p.541         | Addition of description in 10.3.3 (3) Receive data buffer registers 30, 31 (SIRB30, SIRB31)                                                                                               |

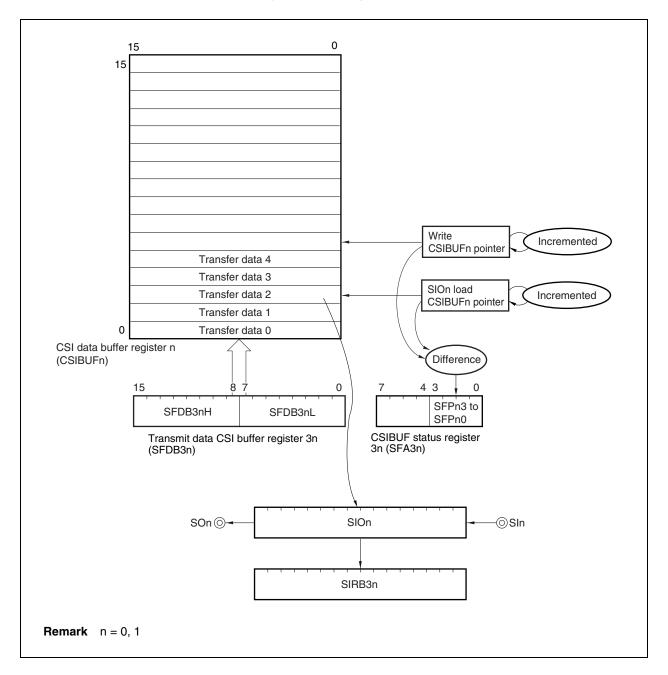

| p.542         | Addition of description in 10.3.3 (4) Transmit data CSI buffer registers 30, 31 (SFDB30, SFDB31)                                                                                          |

| p.544         | Modification of description in 10.3.3 (5) CSIBUF status registers 30, 31 (SFA30, SFA31)                                                                                                   |

| p.549         | Modification of example in Caution 2 in 10.3.4 (2) Baud rate                                                                                                                              |

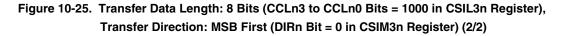

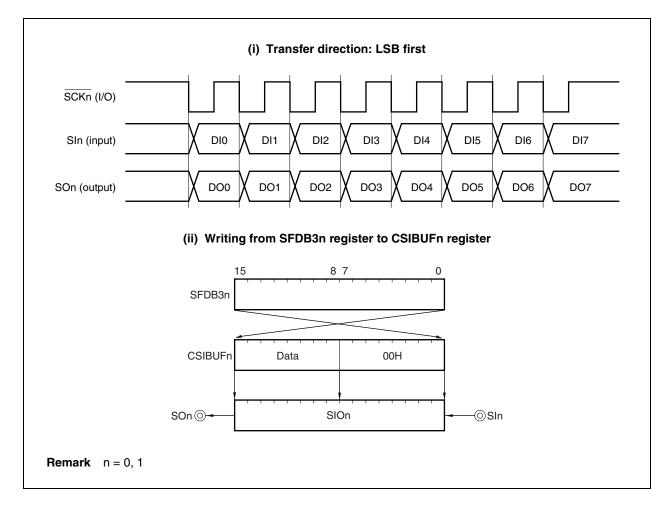

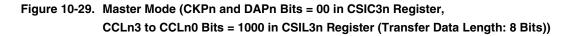

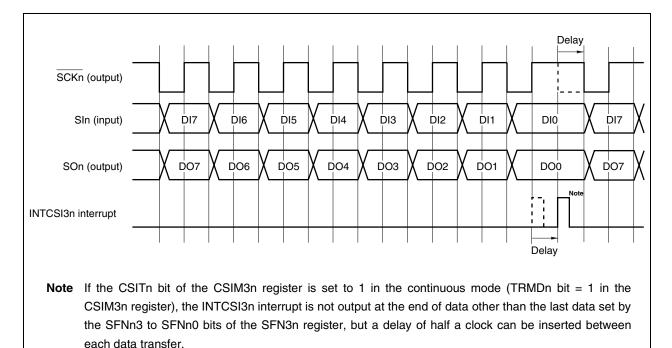

| p.553         | Modification of description in Figure 10-25 Transfer Data Length: 8 Bits (CCLn3 to CCLn0 Bits = 1000 in CSIL3n Register), Transfer Direction: MSB First (DIRn Bit = 0 in CSIM3n Register) |

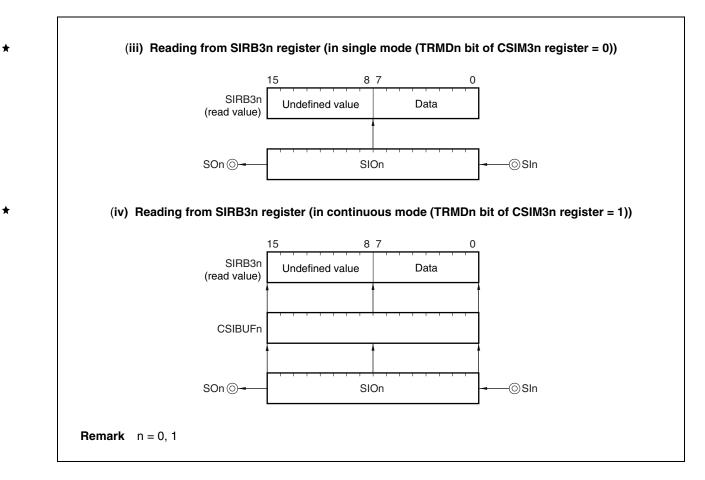

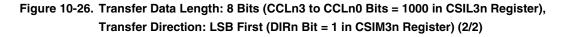

| p.555         | Modification of description in Figure 10-26 Transfer Data Length: 8 Bits (CCLn3 to CCLn0 Bits = 1000 in CSIL3n Register), Transfer Direction: LSB First (DIRn Bit = 1 in CSIM3n Register) |

| p.559         | Deletion of description of 10.3.5 (7) Slave mode                                                                                                                                          |

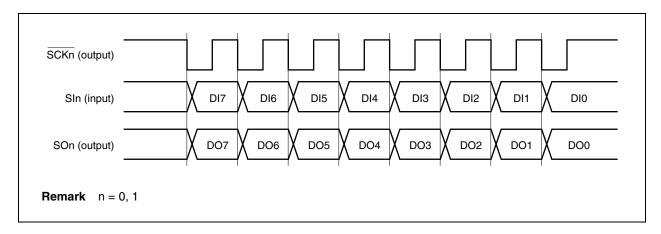

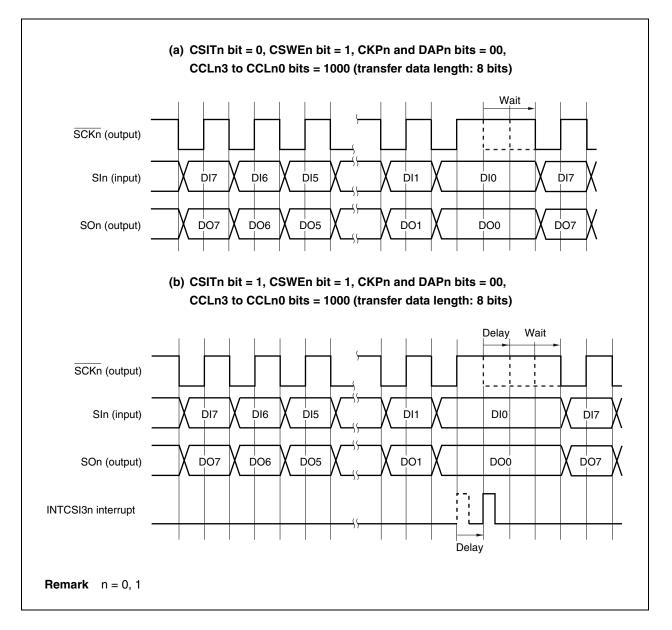

| p.559         | Modification of Figure 10-30 Slave Mode (CKPn and DAPn Bits = 00 in CSIC3n Register, CCLn3 to CCLn0 Bits = 1000 in CSIL3n Register (Transfer Data Length: 8 Bits))                        |

| p.563         | Modification of description in Figure 10-32 Continuous Mode                                                                                                                               |

| p.564         | Modification of description in 10.3.5 (11) Transmission mode                                                                                                                              |

| p.564         | Addition of description in 10.3.5 (12) Reception mode                                                                                                                                     |

| p.567         | Deletion of description in 10.3.5 (16) (a) SCKn pin                                                                                                                                       |

| p.567         | Modification of description in Table 10-8 Default Output Level of SCKn Pin                                                                                                                |

| pp.568 to 573 | Modification of description of (1) to (12) in 10.3.6 Usage                                                                                                                                |

| p.575         | Addition of Caution in 11.1 Overview                                                                                                                                                      |

# Major Revisions in This Edition (4/4)

| Page                                         | Description                                                                                                                                                                       |

|----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| p.578                                        | Addition of items in Table 11-2 Correspondence Between Requests and Decoded Values                                                                                                |

| p.589                                        | Addition of description in 11.4.1 (3) UF0 EPNAK register (UF0EN)                                                                                                                  |

| p.599                                        | Deletion of description in 11.4.1 (9) UF0 EP status 1 register (UF0EPS1)                                                                                                          |

| p.601                                        | Modification of description in 11.4.1 (11) UF0 INT status 0 register (UF0IS0)                                                                                                     |

| p.629                                        | Modification of description in 11.4.1 (34) UF0 mode status register (UF0MODS)                                                                                                     |

| p.665                                        | Modification of description in 11.4.3 (2) UF0 EP0 status register L (UF0E0SL)                                                                                                     |

| p.672                                        | Modification of description in 11.4.3 (9) UF0 address register (UF0ADRS)                                                                                                          |

| p.673                                        | Modification of description in 11.4.3 (10) UF0 configuration register (UF0CNF)                                                                                                    |

| p.674                                        | Modification of description in 11.4.3 (11) UF0 interface 0 register (UF0IF0)                                                                                                      |

| p.675                                        | Modification of description in 11.4.3 (12) UF0 interface 1 to 4 registers (UF0IF1 to UF0IF4)                                                                                      |

| p.677                                        | Modification of Caution 2 in 11.4.3 (14) UF0 device descriptor registers 0 to 17 (UF0DD0 to UF0DD17)                                                                              |

| p.678                                        | Modification of Caution 2 in 11.4.3 (15) UF0 configuration/interface/endpoint descriptor registers 0 to 255 (UF0CIE0 to UF0CIE255)                                                |

| p.680                                        | Modification of Caution in 11.4.4 (1) USB function 0 DMA channel select register (UF0CS)                                                                                          |

| p.686                                        | Deletion of Caution in Table 11-8 FW-Supported Standard Requests                                                                                                                  |

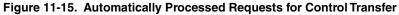

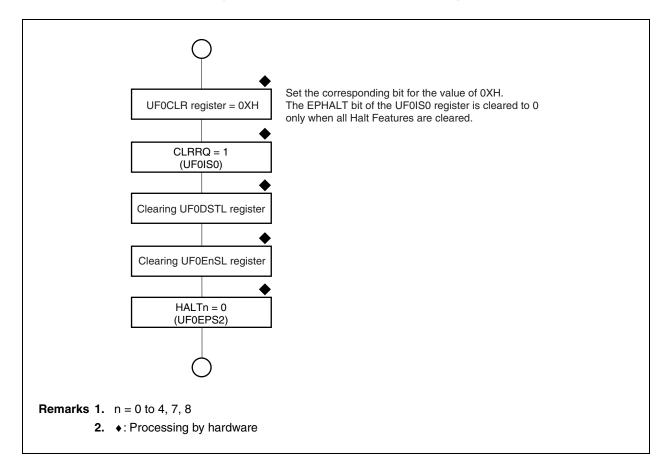

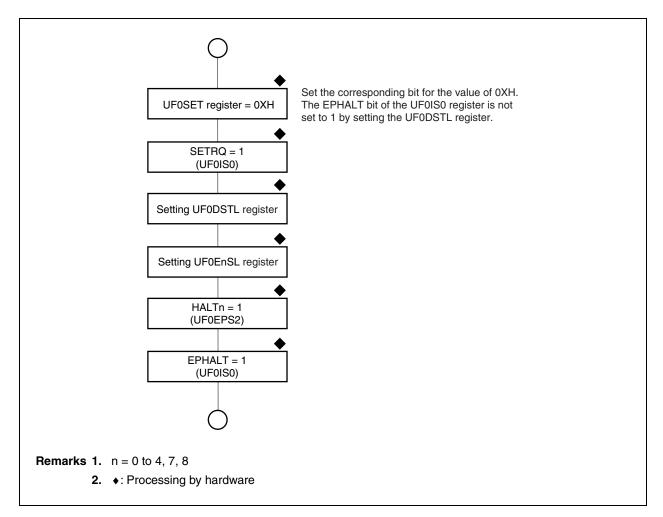

| p.692                                        | Modification of description in Figure 11-15 Automatically Processed Requests for Control Transfer                                                                                 |

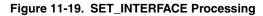

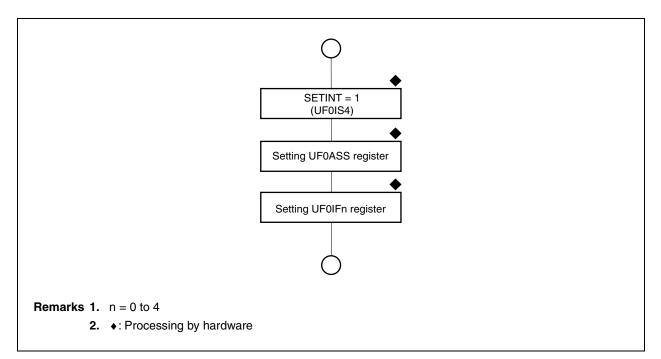

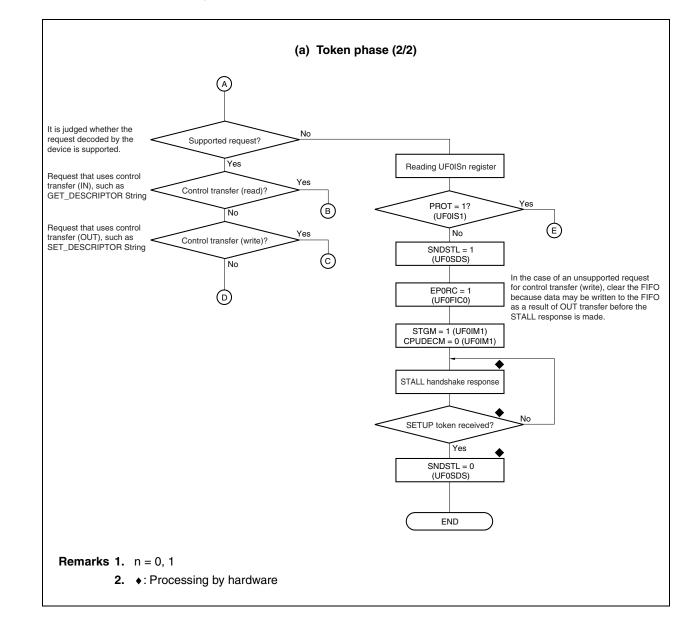

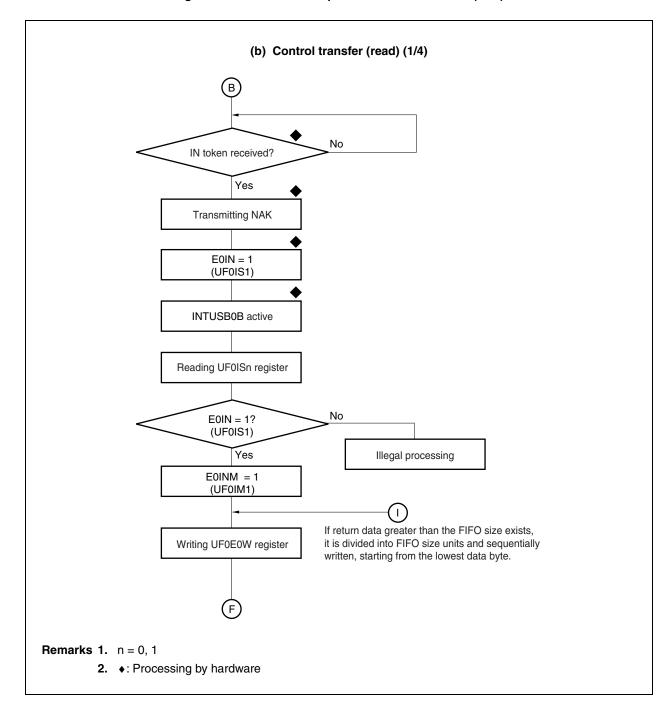

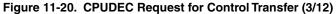

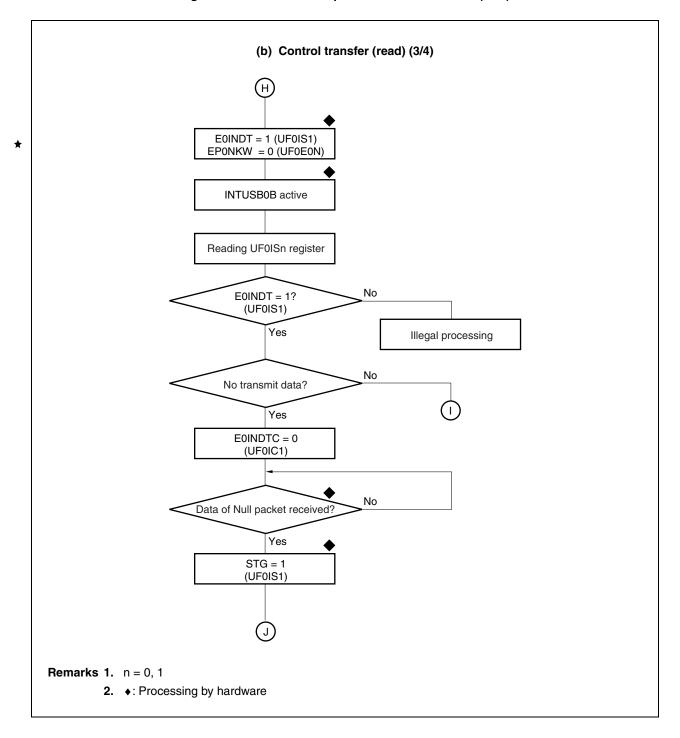

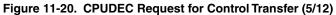

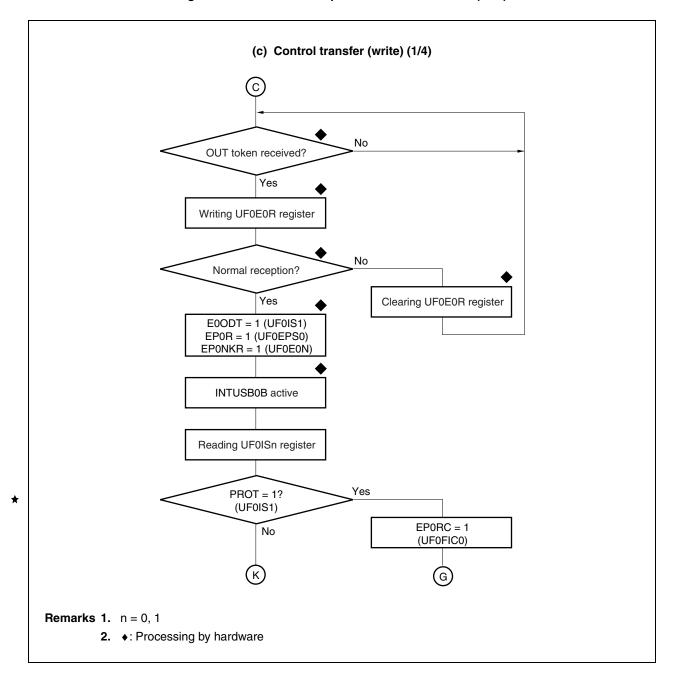

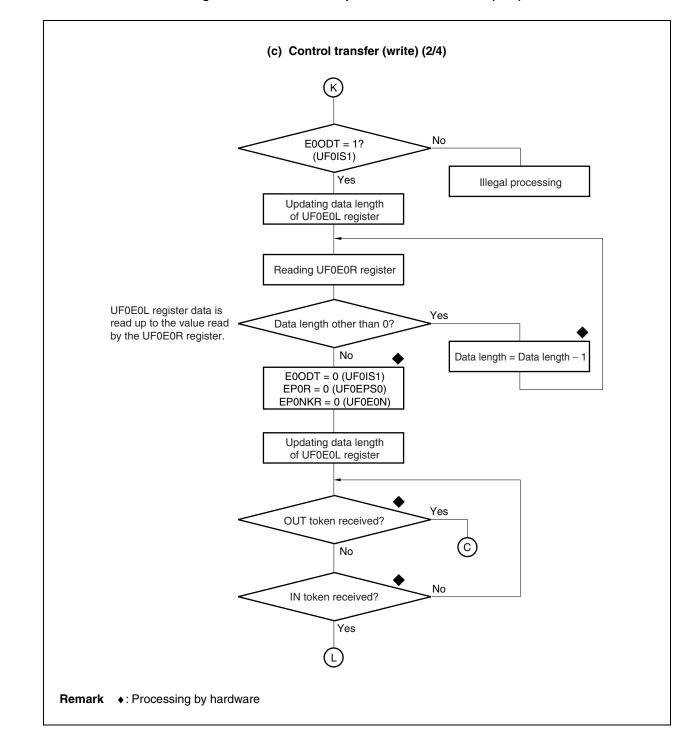

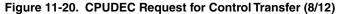

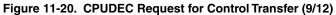

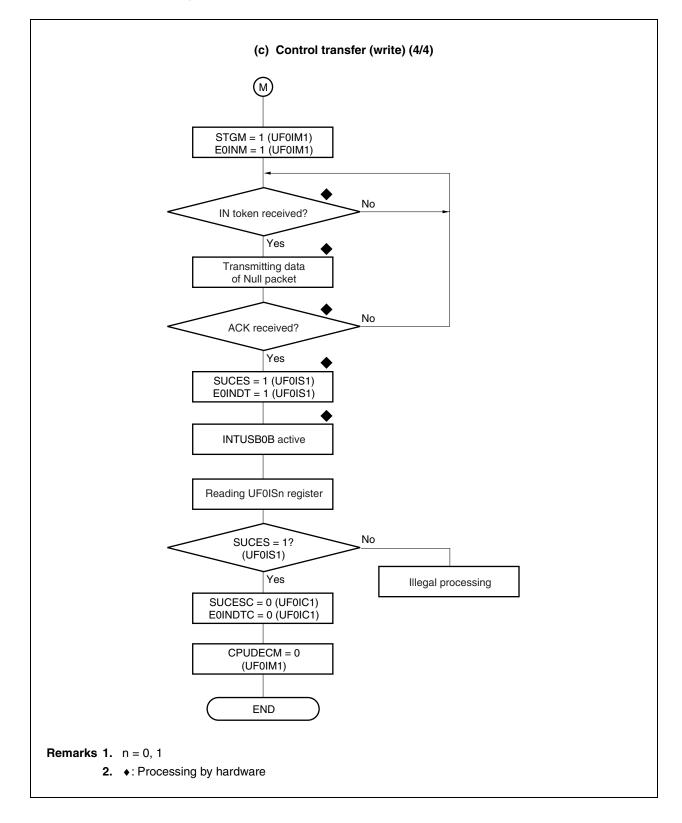

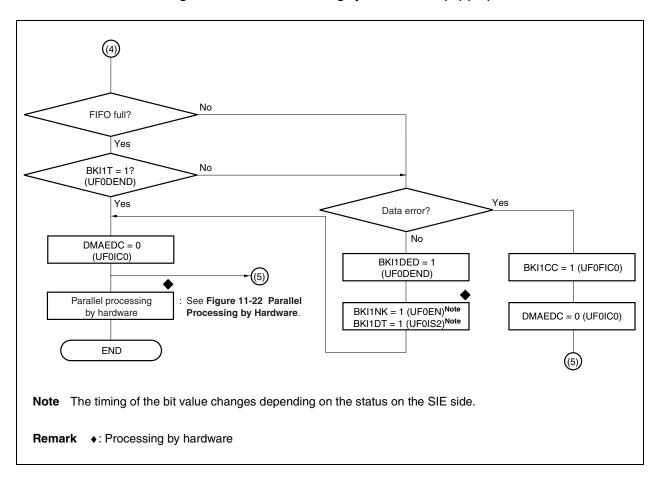

| pp.696, 697, 699,<br>700, 702 to 704,<br>706 | Modification of description in Figure 11-20 CPUDEC Request for Control Transfer                                                                                                   |

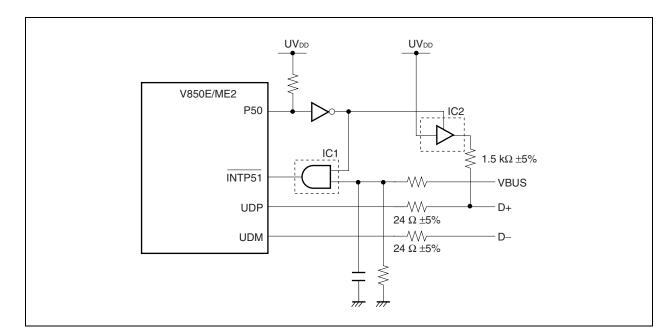

| p.733                                        | Modification of description in Figure 11-30 USB Connection Example                                                                                                                |

| p.739                                        | Addition of value when fx = 150 MHz in Table 12-1 Setting of A/D Conversion Operation Time                                                                                        |

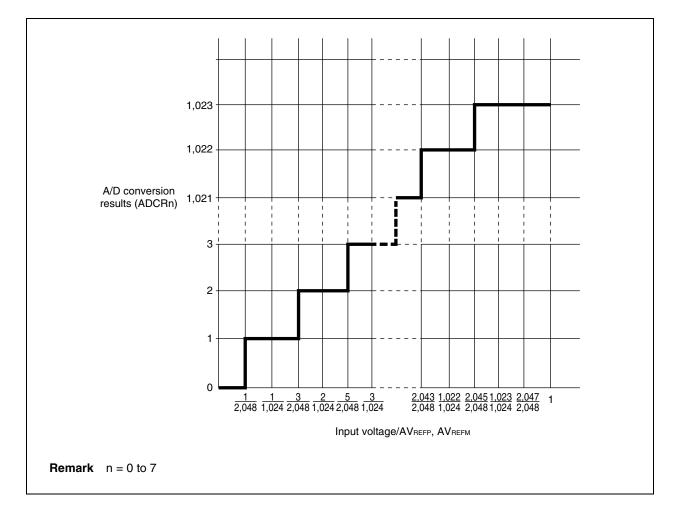

| p.763                                        | Addition of 12.9 How to Read A/D Converter Characteristics Table                                                                                                                  |

| p.767                                        | Modification of repeat frequency in 13.1 Features                                                                                                                                 |

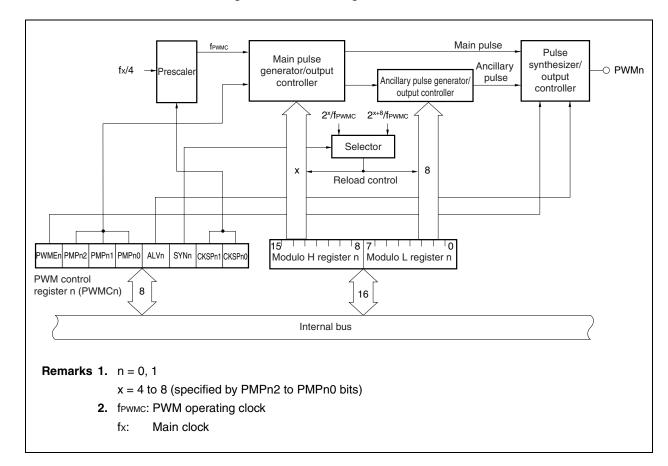

| p.768                                        | Modification of description in Figure 13-1 Block Diagram of PWM Unit                                                                                                              |

| p.770                                        | Modification of description in 13.3 (1) PWM control registers 0 and 1 (PWMC0 and PWMC1)                                                                                           |

| p.775                                        | Modification of description in 13.4.2 (1) Setting for starting PWM operation                                                                                                      |

| p.779                                        | Modification of description in Table 13-1 Repeat Cycle of PWMn                                                                                                                    |

| p.839                                        | Modification of Caution in 14.3.8 Port DH                                                                                                                                         |

| p.843                                        | Modification of Caution and description on bit 0 in 14.3.8 (2) (c) Port DH function control register (PFCDH)                                                                      |

| p.853                                        | Addition to Caution in 14.3.10 (2) (c) Port CT function control register (PFCCT)                                                                                                  |

| p.866                                        | Addition of noise elimination width when fx = 150 MHz in Table 14-4 Relationship Between NCW1n Register Set Value and Noise Elimination Width                                     |

| p.873                                        | Modification of value of program counter (PC) after reset in Table 15-2 Initial Value of CPU, Internal Data RAM, Internal Instruction RAM, and On-Chip Peripheral I/O After Reset |

| p.880                                        | Modification of description in 16.1.1 (7) Mask function                                                                                                                           |

| p.885                                        | Addition of CHAPTER 17 ELECTRICAL SPECIFICATIONS (TARGET VALUES)                                                                                                                  |

| p.928                                        | Addition of CHAPTER 18 PACKAGE DRAWING                                                                                                                                            |

| p.929                                        | Addition of CHAPTER 19 RECOMMENDED SOLDERING CONDITIONS                                                                                                                           |

| p.952                                        | Addition to Note in B.2 Instruction Set (in Alphabetical Order)                                                                                                                   |

| p.953                                        | Addition of APPENDIX C REVISION HISTORY                                                                                                                                           |

The mark  $\star$  shows major revised points.

#### INTRODUCTION

ReadersThis manual is intended for users who wish to understand the functions of the<br/>V850E/ME2 (μPD703111) to design application systems using the V850E/ME2.

Purpose

The purpose of this manual is for users to gain an understanding of the hardware functions of the V850E/ME2.

Organization The V850E/ME2 User's Manual is divided into two parts: Hardware (this manual) and Architecture (V850E1 Architecture User's Manual). The organization of each manual is as follows:

| Hardware |  |

|----------|--|

|          |  |

- Pin functions

- CPU function

- Internal peripheral functions

- Electrical specifications (target value)

- Data type

- Register set

- Instruction format and instruction set

- · Interrupts and exceptions

- Pipeline operation

How to Read This Manual It is assumed that the readers of this manual have general knowledge in the fields of electrical engineering, logic circuits, and microcontrollers.

- To find the details of a register where the name is known

→Refer to APPENDIX A REGISTER INDEX.

- To understand the details of an instruction function

→Refer to the V850E1 Architecture User's Manual.

To know the electrical specifications of the V850E/ME2

- $\rightarrow$  Refer to CHAPTER 17 ELECTRICAL SPECIFICATIONS (TARGET VALUES).

- To understand the overall functions of the V850E/ME2

→Read this manual according to the CONTENTS.

- How to interpret the register format

- $\rightarrow$ For a bit whose bit number is enclosed in brackets, its bit name is defined as a reserved word in the device file.

| Conventions       | Data significance:<br>Active low representation:<br>Memory map address: | Higher digits on the left and lower digits on the right                                |

|-------------------|-------------------------------------------------------------------------|----------------------------------------------------------------------------------------|

|                   | Note:                                                                   | Footnote for item marked with <b>Note</b> in the text                                  |

|                   | Caution:                                                                | Information requiring particular attention                                             |

|                   | Remark:                                                                 | Supplementary information                                                              |

|                   | Numeric representation:                                                 | Binary xxxx or xxxxB                                                                   |

|                   |                                                                         | Decimal xxxx                                                                           |

|                   |                                                                         | Hexadecimal xxxxH                                                                      |

|                   | Prefix indicating power of 2                                            |                                                                                        |

|                   | (address space, memory                                                  |                                                                                        |

|                   | capacity):                                                              | K (kilo): 2 <sup>10</sup> = 1,024                                                      |

|                   |                                                                         | M (mega): 2 <sup>20</sup> = 1,024 <sup>2</sup>                                         |

|                   |                                                                         | G (giga): 2 <sup>30</sup> = 1,024 <sup>3</sup>                                         |

|                   | Data type:                                                              | Word 32 bits                                                                           |

|                   |                                                                         | Halfword 16 bits                                                                       |

|                   |                                                                         | Byte 8 bits                                                                            |

| Related documents | The related documents indica<br>However, preliminary versions           | ted in this publication may include preliminary versions.<br>s are not marked as such. |

#### Document related to V850E/ME2

| Document Name                     | Document No. |

|-----------------------------------|--------------|

| V850E1 Architecture User's Manual | U14559E      |

| V850E/ME2 Hardware User's Manual  | This manual  |

# Document related to development tools (User's Manuals)

| Document Name                             |                   | Document No. |

|-------------------------------------------|-------------------|--------------|

| CA850 (Ver. 2.50) (C Compiler Package)    | Operation         | U16053E      |

|                                           | C Language        | U16054E      |

|                                           | PM plus           | U16055E      |

|                                           | Assembly Language | U16042E      |

| RX850 (Ver. 3.13 or Later) (Real-Time OS) | Basics            | U13430E      |

|                                           | Installation      | U13410E      |

|                                           | Technical         | U13431E      |

| RX850 Pro (Ver. 3.15) (Real-Time OS)      | Basics            | U13773E      |

|                                           | Installation      | U13774E      |

|                                           | Technical         | U13772E      |

| RD850 (Ver. 3.01) (Task Debugger)         |                   | U13737E      |

| RD850 Pro (Ver. 3.01) (Task Debugger)     |                   | U13916E      |

#### CONTENTS

| СНАРТЕ | R 1 INTRODUCTION             |                                                                         |

|--------|------------------------------|-------------------------------------------------------------------------|

| 1.1    | Outline                      |                                                                         |

| 1.2    | Features                     |                                                                         |

| 1.3    | Applications                 |                                                                         |

| 1.4    | Ordering Information         |                                                                         |

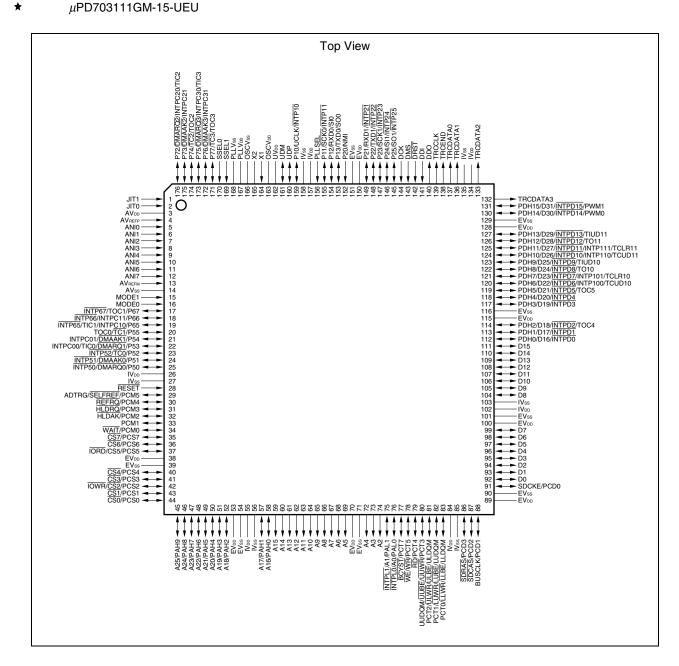

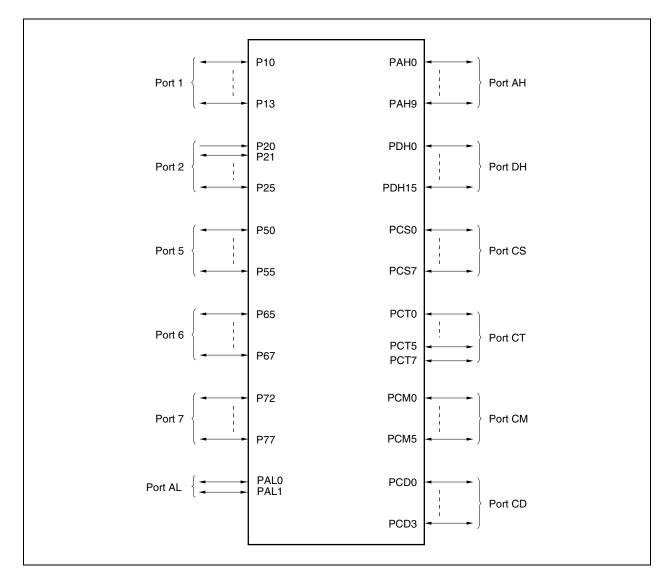

| 1.5    | Pin Configuration            |                                                                         |

| 1.6    | Function Blocks              |                                                                         |

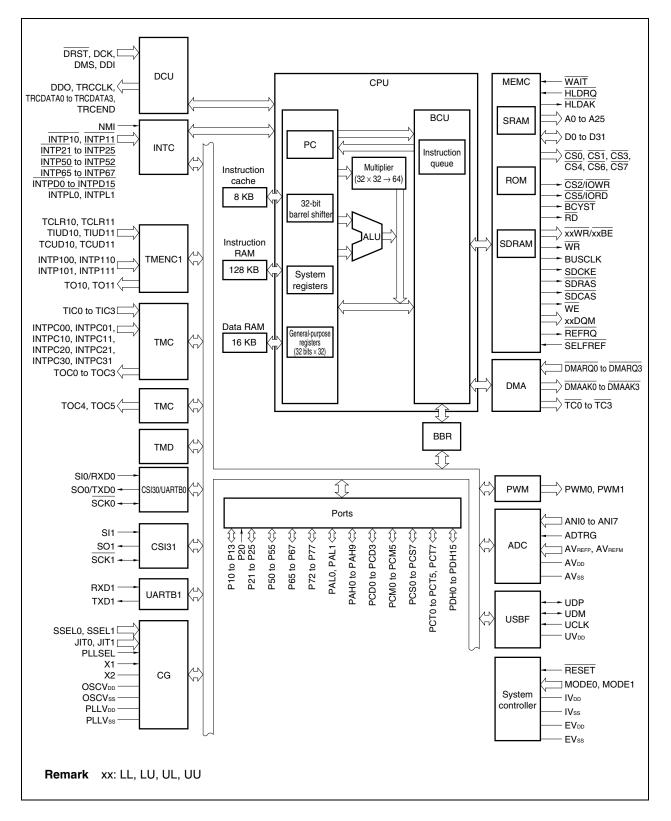

|        | 1.6.1 Internal block diagra  | am34                                                                    |

|        | 1.6.2 On-chip units          |                                                                         |

| СНАРТЕ | R 2 PIN FUNCTIONS            |                                                                         |

| 2.1    | List of Pin Functions        |                                                                         |

| 2.2    | Pin Status                   |                                                                         |

| 2.3    | Description of Pin Func      | tions48                                                                 |

| 2.4    |                              | commended Connection of Unused Pins64                                   |

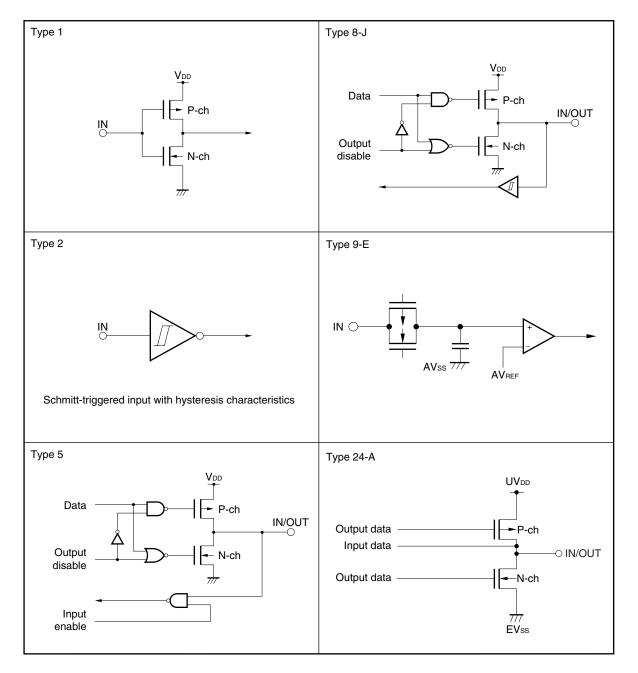

| 2.5    | Pin I/O Circuits             |                                                                         |

|        |                              |                                                                         |

| СНАРТЕ | R 3 CPU FUNCTION             |                                                                         |

| 3.1    | Features                     |                                                                         |

| 3.2    | CPU Register Set             |                                                                         |

|        | 3.2.1 Program register se    | et70                                                                    |

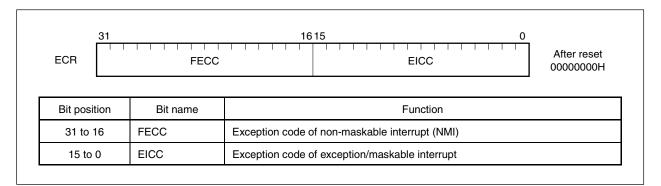

|        | 3.2.2 System register set    |                                                                         |

| 3.3    | Operating Modes              |                                                                         |

|        | 3.3.1 Operating modes        |                                                                         |

|        | 3.3.2 Operating mode sp      | ecification74                                                           |

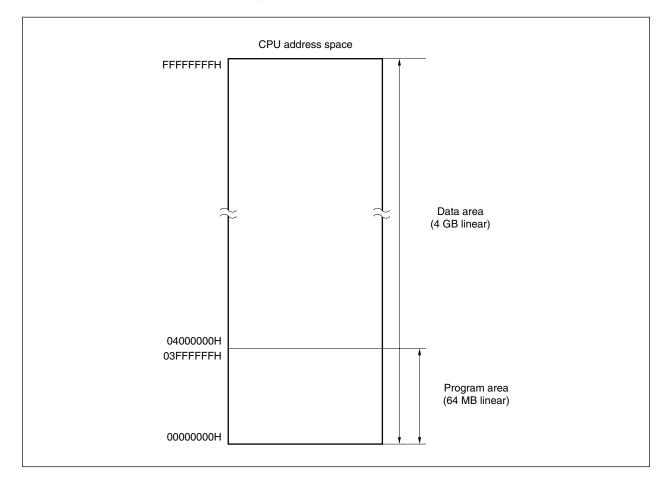

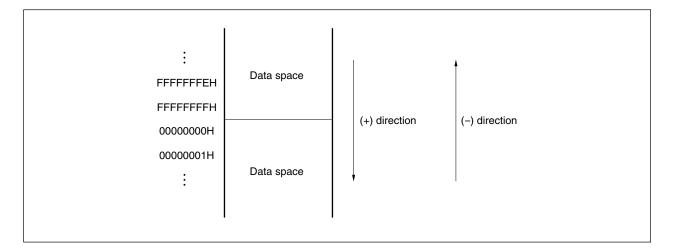

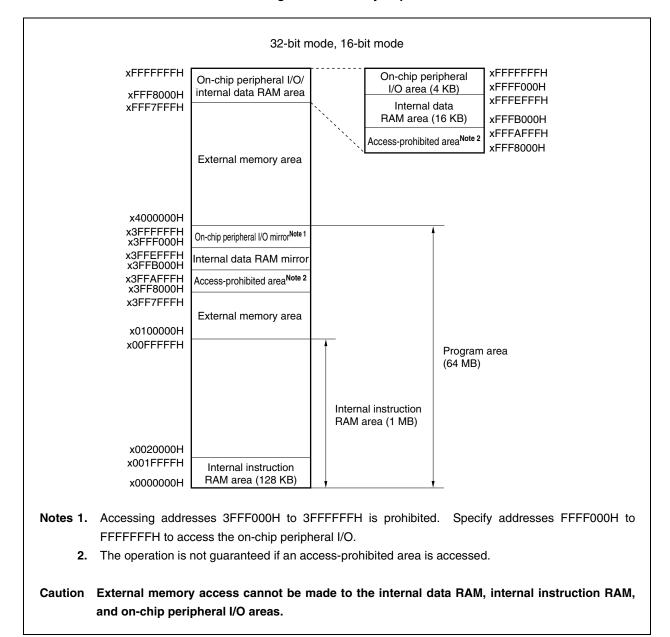

| 3.4    | Address Space                | 75                                                                      |

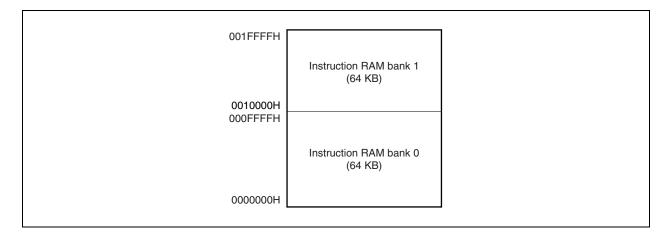

|        | 3.4.1 CPU address space      | 975                                                                     |

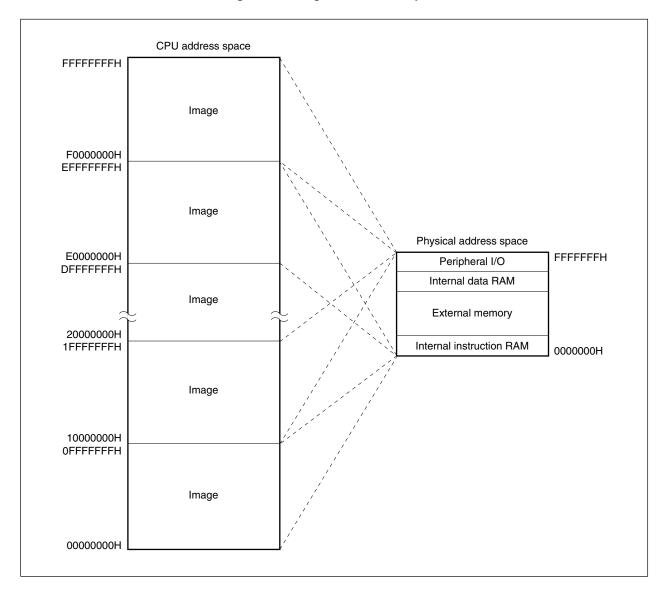

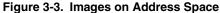

|        | 3.4.2 Image                  |                                                                         |

|        | 3.4.3 Wrap-around of CP      | U address space77                                                       |

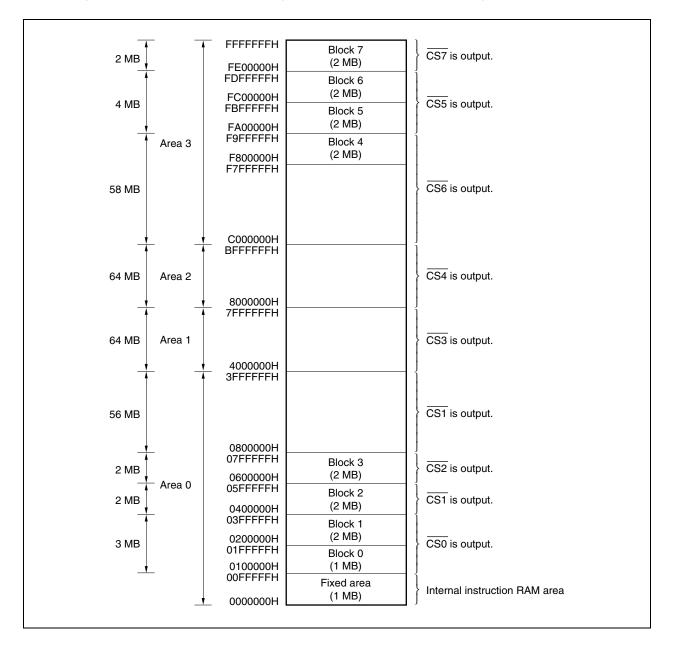

|        | 3.4.4 Memory map             |                                                                         |

|        | 3.4.5 Area                   |                                                                         |

|        | 3.4.6 Recommended use        | of address space                                                        |

|        | 3.4.7 Peripheral I/O regis   | ters85                                                                  |

|        | 3.4.8 Specific registers     |                                                                         |

|        | 3.4.9 System wait control    | I register (VSWC)111                                                    |

|        | 3.4.10 Initialization sequer | nce112                                                                  |

| СНАВТЕ |                              | UNCTION                                                                 |

| -      |                              |                                                                         |

| 4.1    |                              |                                                                         |

| 4.2    |                              |                                                                         |

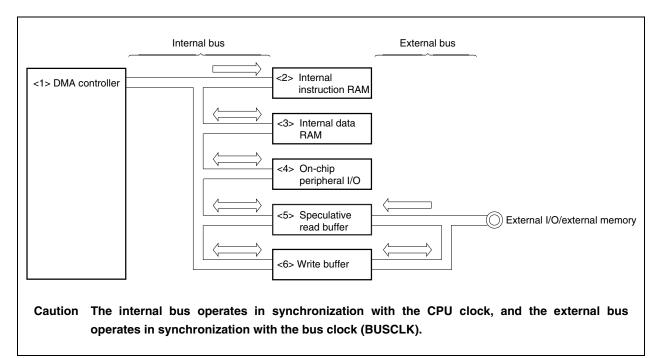

|        | -                            | ternal instruction RAM, internal data RAM, and peripheral I/O access115 |

| 4.3    | Memory Block Function        |                                                                         |

|       | 4.3.1            | Chip select control function                                              | 117 |

|-------|------------------|---------------------------------------------------------------------------|-----|

| 4.4   | Bus C            | ycle Type Control Function                                                | 120 |

|       | 4.4.1            | Bus cycle type configuration registers 0, 1 (BCT0, BCT1)                  | 121 |

| 4.5   | Bus A            | ccess                                                                     | 122 |

|       | 4.5.1            | Number of access clocks                                                   | 122 |

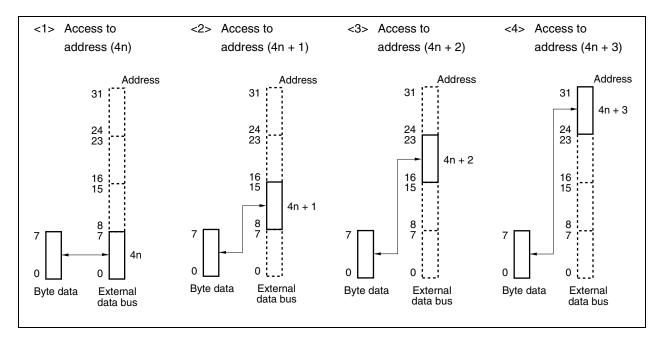

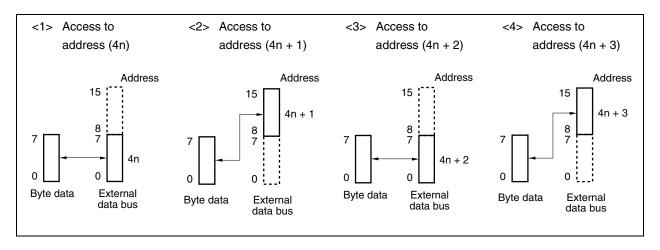

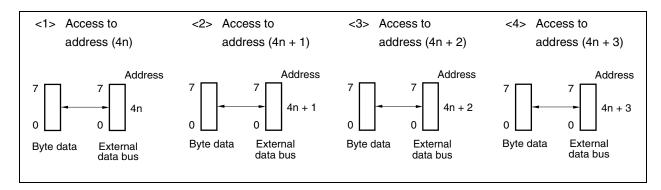

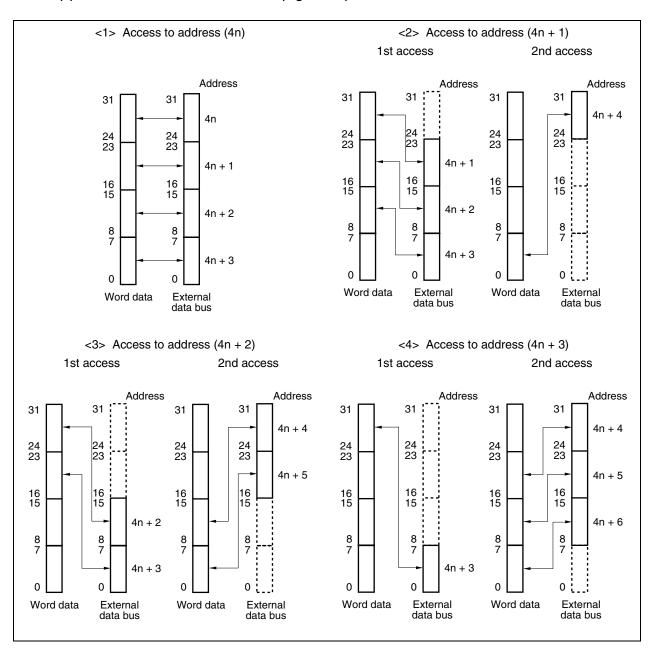

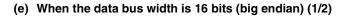

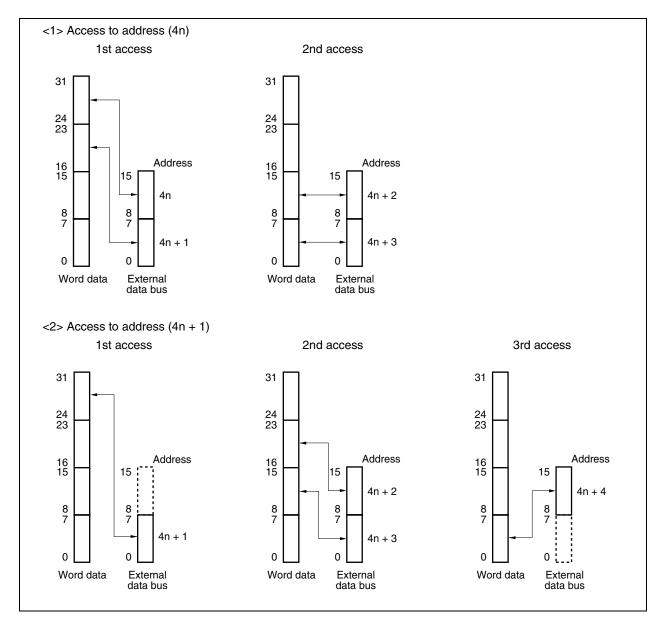

|       | 4.5.2            | Bus sizing function                                                       | 123 |

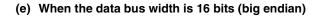

|       | 4.5.3            | Endian control function                                                   | 124 |

|       | 4.5.4            | Big endian method usage restrictions in NEC Electronics development tools |     |

|       | 4.5.5            | Bus width                                                                 | 127 |

|       | 4.5.6            | Data read control function                                                | 146 |

| 4.6   |                  | lock Control Function                                                     |     |

| 4.7   | Wait F           | unction                                                                   |     |

|       | 4.7.1            | Programmable wait function                                                |     |

|       | 4.7.2            | External wait function                                                    |     |

|       | 4.7.3            | Relationship between programmable wait and external wait                  |     |

|       | 4.7.4            | Bus cycles in which wait function is valid                                |     |

| 4.8   |                  | tate Insertion Function                                                   |     |

| 4.9   |                  | ction Cache Function                                                      | -   |

|       | 4.9.1            | Cache configuration register (BHC)                                        |     |

|       | 4.9.2            | 8 KB 2-way set associative cache                                          |     |

|       | 4.9.3            | LRU algorithm                                                             |     |

|       | 4.9.4            | Instruction cache control function                                        |     |

|       | 4.9.5            | Tag clear function                                                        |     |

| 4 10  | 4.9.6            | Auto fill function (way 0 only)al Instruction RAM Control Function        |     |

| 4.10  |                  |                                                                           |     |

|       | 4.10.1           | Internal instruction RAM mode register (IRAMM)                            |     |

|       | 4.10.2<br>4.10.3 | Cautions                                                                  |     |

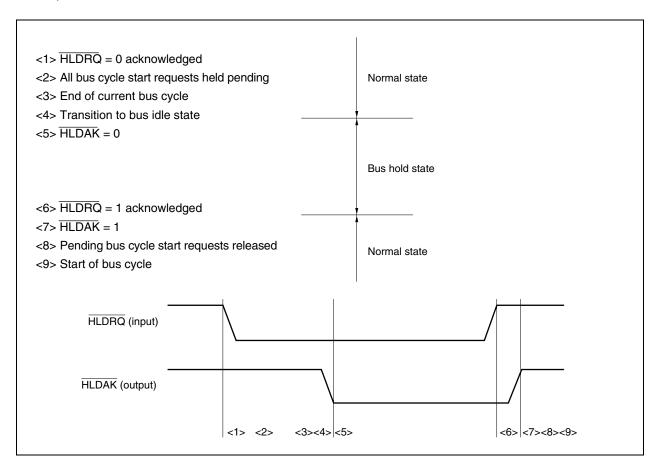

| 4 1 1 |                  | old Function                                                              |     |

| 4.11  | 4.11.1           | Function outline                                                          |     |

|       | 4.11.2           | Bus hold procedure                                                        |     |

|       | 4.11.3           | Operation in power-save mode                                              |     |

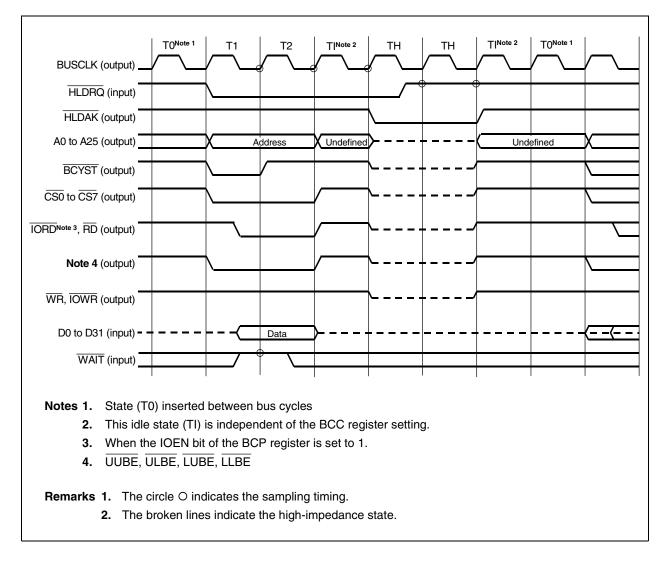

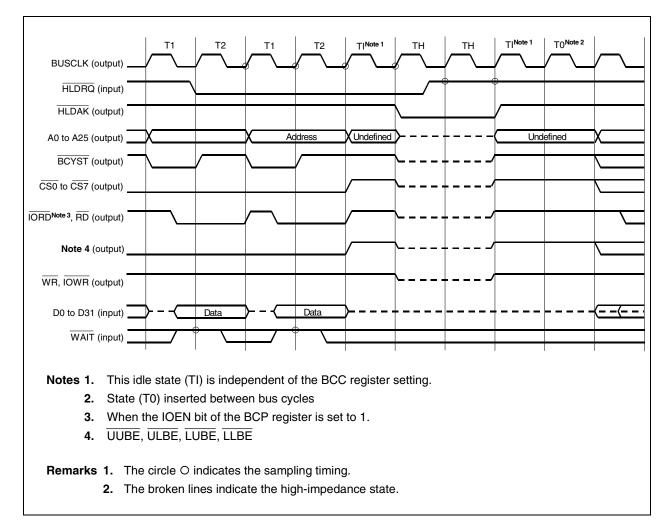

|       | 4.11.4           | Bus hold timing                                                           |     |

|       | 4.11.5           | Bus hold timing (SRAM)                                                    |     |

|       | 4.11.6           | Bus hold timing (SDRAM)                                                   |     |

| 4.12  | -                | riority Order                                                             |     |

|       |                  | dary Operation Conditions                                                 |     |

|       | 4.13.1           | Program space                                                             |     |

|       | 4.13.2           | Data space                                                                |     |

| 4.14  | Timing           | g at Which T0 State Is Not Inserted                                       |     |

|       |                  |                                                                           |     |

|       |                  | MEMORY ACCESS CONTROL FUNCTION                                            |     |

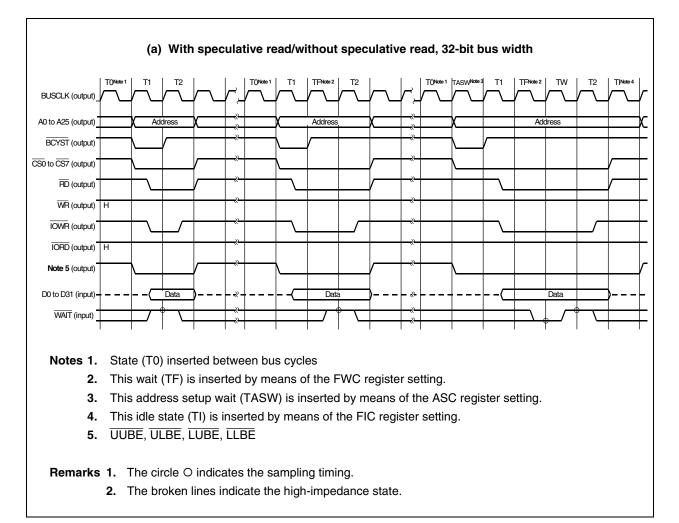

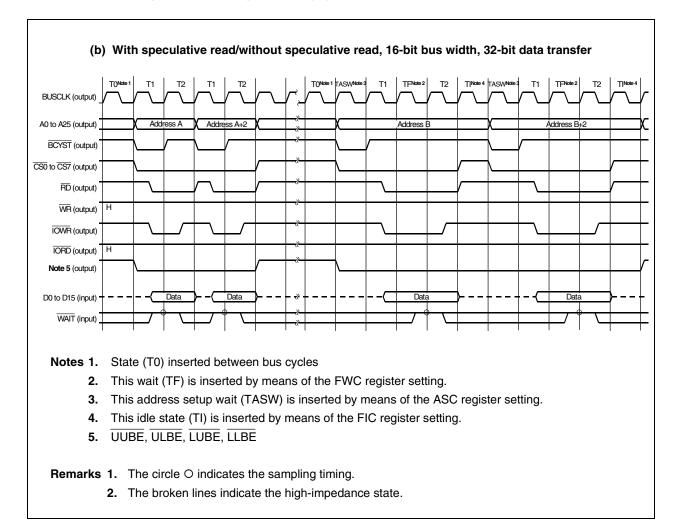

| 5.1   | SRAM             | I, External ROM, External I/O Interface                                   |     |

|       | 5.1.1            | Features                                                                  |     |

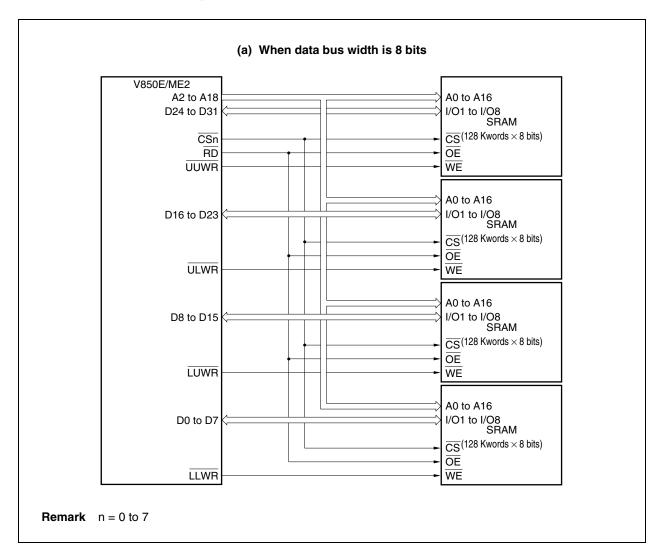

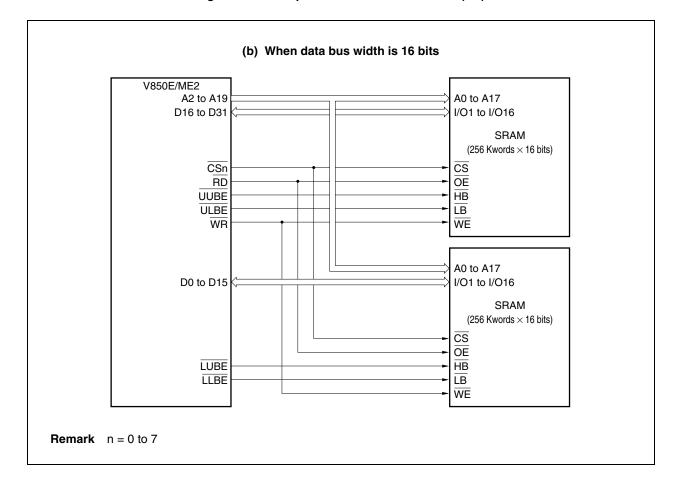

|       | 5.1.2            | SRAM connection                                                           |     |

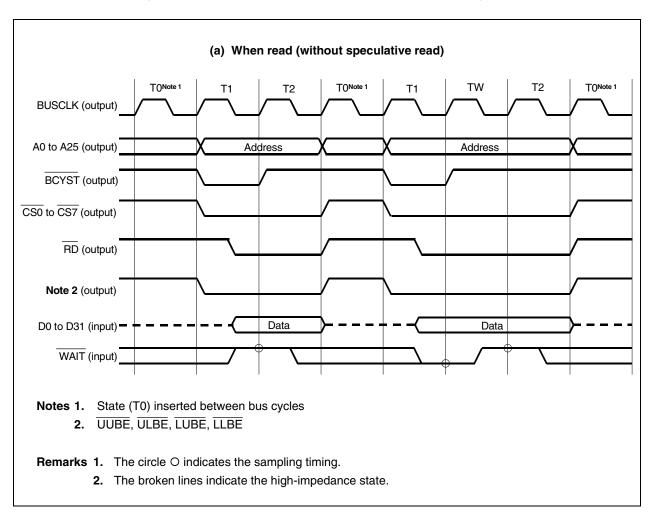

|       | 5.1.3            | SRAM, external ROM, external I/O access                                   |     |

| 5.2   | Page I           | ROM Controller (ROMC)                                                     |     |

$\star$

|               | 5.2.1 Features                                                          |      |

|---------------|-------------------------------------------------------------------------|------|

|               | 5.2.2 Page ROM connection                                               | 197  |

|               | 5.2.3 On-page/off-page judgment                                         |      |

|               | 5.2.4 Page ROM configuration register (PRC)                             |      |

|               | 5.2.5 Page ROM access                                                   |      |

| 5.3           | DRAM Controller (SDRAM)                                                 |      |

|               | 5.3.1 Features                                                          |      |

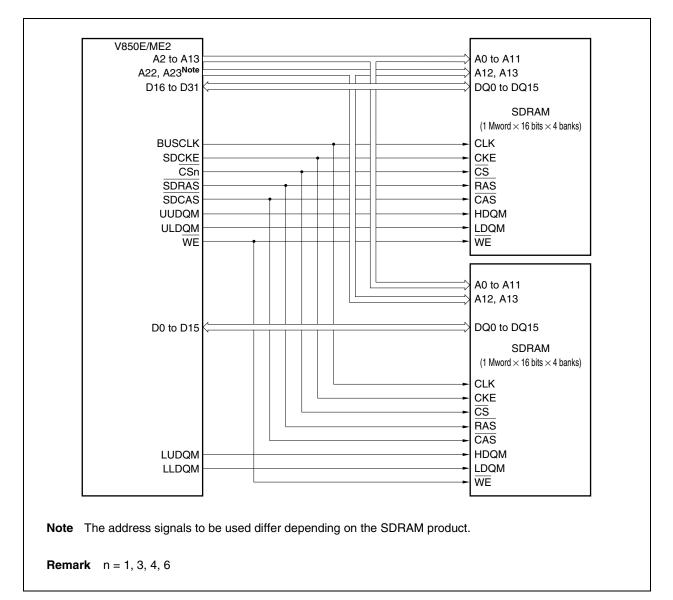

|               | 5.3.2 SDRAM connection                                                  |      |

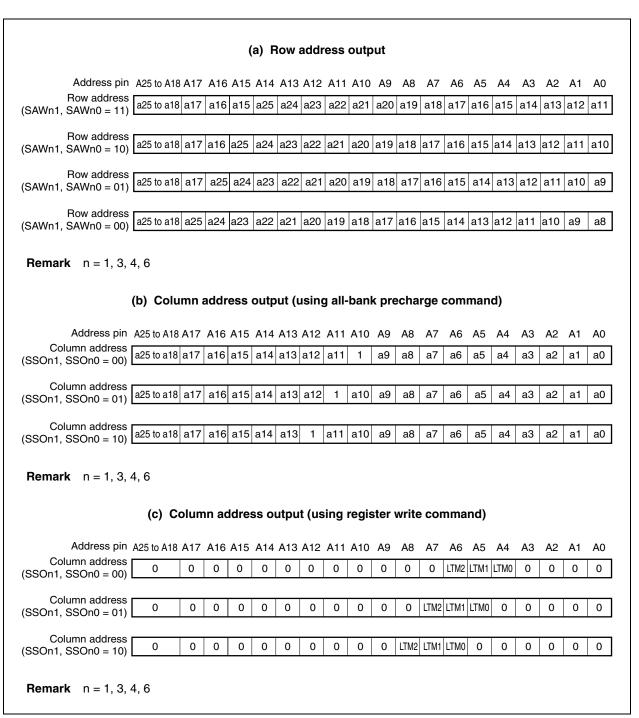

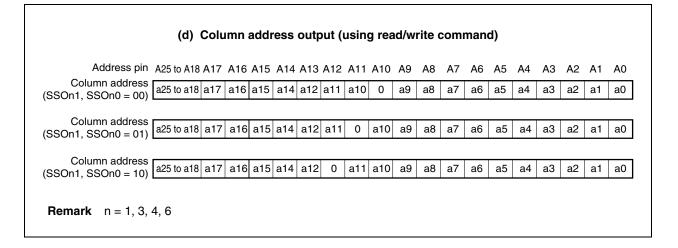

|               | 5.3.3 Address multiplex function                                        |      |

|               | 5.3.4 SDRAM configuration registers 1, 3, 4, 6 (SCR1, SCR3, SCR4, SCR6) | )209 |

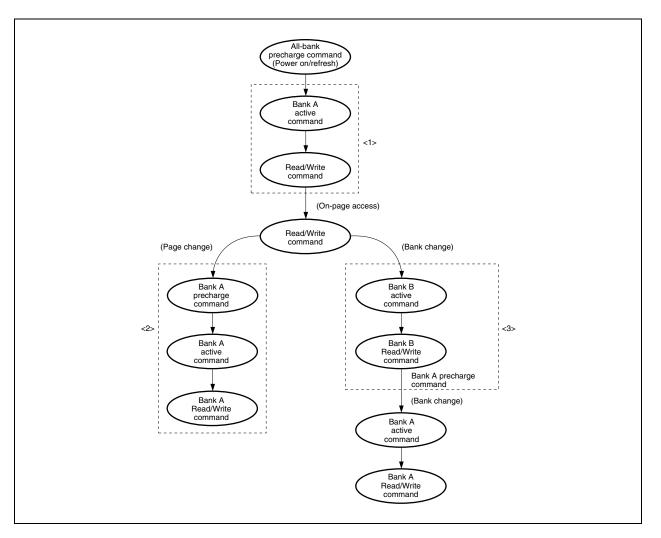

|               | 5.3.5 SDRAM access                                                      | 212  |

|               | 5.3.6 Refresh control function                                          | 236  |

|               | 5.3.7 Self-refresh control function                                     | 241  |

|               | 5.3.8 SDRAM initialization sequence                                     | 243  |

| CHAPTE<br>6.1 | ER 6 DMA FUNCTIONS (DMA CONTROLLER)                                     |      |

| 6.2           | Configuration                                                           | 247  |

| 6.3           | Control Registers                                                       | 248  |

|               | 6.3.1 DMA source address registers 0 to 3 (DSA0 to DSA3)                | 248  |

|               | 6.3.2 DMA destination address registers 0 to 3 (DDA0 to DDA3)           | 250  |

|               | 6.3.3 DMA transfer count registers 0 to 3 (DBC0 to DBC3)                | 252  |

|               | 6.3.4 DMA addressing control registers 0 to 3 (DADC0 to DADC3)          | 253  |

|               | 6.3.5 DMA channel control registers 0 to 3 (DCHC0 to DCHC3)             | 256  |

|               | 6.3.6 DMA terminal count output control register (DTOC)                 | 259  |

|               | 6.3.7 DMA trigger factor registers 0 to 3 (DTFR0 to DTFR3)              |      |

|               | 6.3.8 DMA interface control register (DIFC)                             |      |

| 6.4           | Transfer Modes                                                          | 267  |

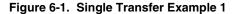

|               | 6.4.1 Single transfer mode                                              |      |

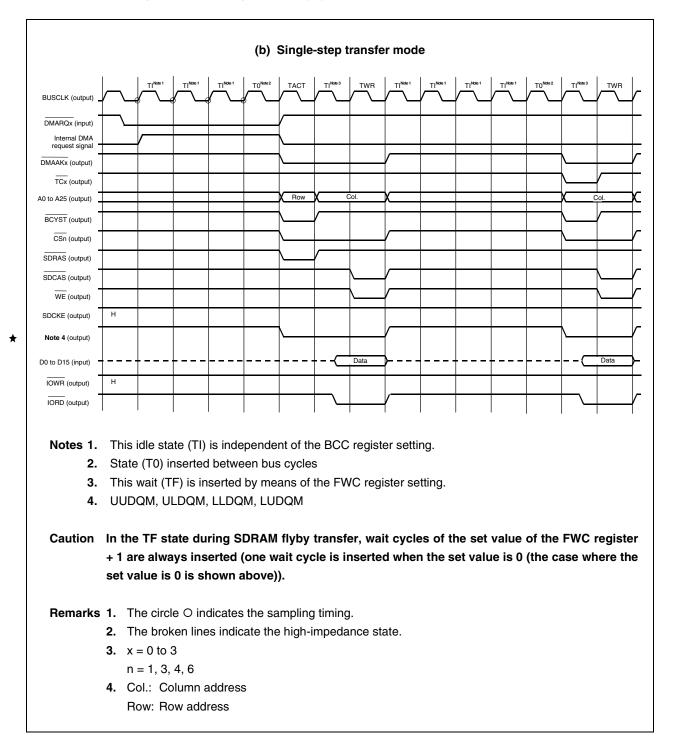

|               | 6.4.2 Single-step transfer mode                                         |      |

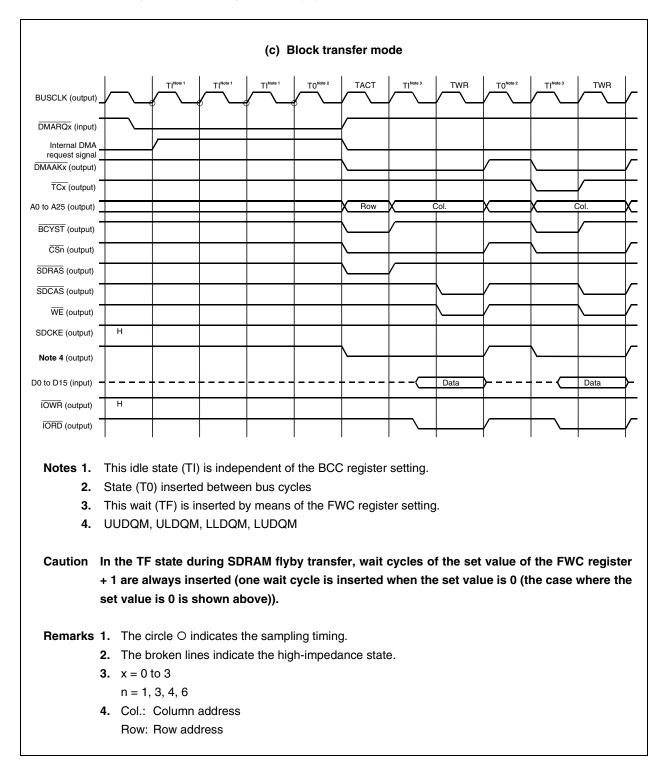

|               | 6.4.3 Block transfer mode                                               | 270  |

| 6.5           | Transfer Types                                                          | 271  |

|               | 6.5.1 2-cycle transfer                                                  |      |

|               | 6.5.2 Flyby transfer                                                    |      |

| 6.6           | Transfer Object                                                         |      |

|               | 6.6.1 Transfer type and transfer object                                 |      |

|               | 6.6.2 External bus cycles during DMA transfer                           |      |

| 6.7           | DMA Channel Priorities                                                  |      |

| 6.8           | Next Address Setting Function                                           |      |

| 6.9           | DMA Transfer Start Factors                                              |      |

| 6.10          |                                                                         |      |

| 6.11          |                                                                         |      |

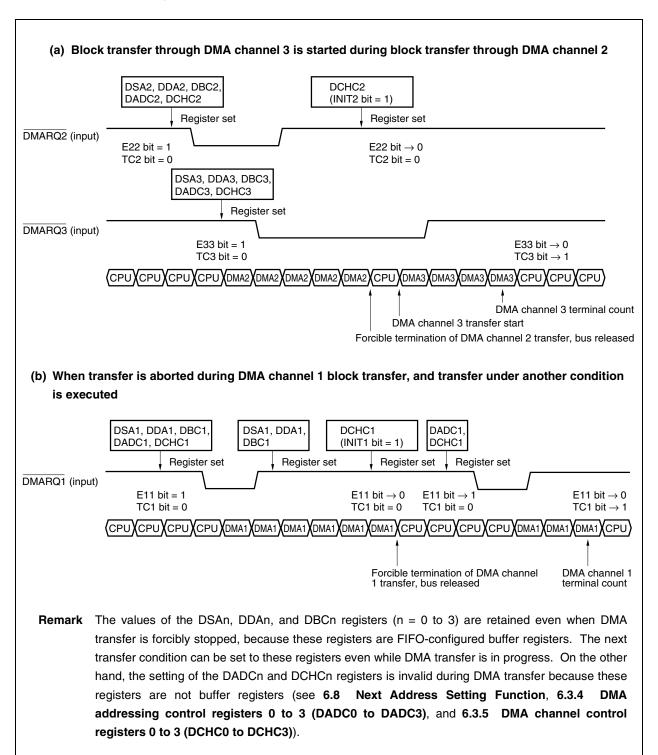

|               | Forcible Termination                                                    |      |

|               | Times Related to DMA Transfer                                           |      |

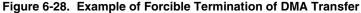

|               | Maximum Response Time for DMA Transfer Request                          |      |

| 6.15          | Cautions                                                                |      |

|               | 6.15.1 Interrupt factors                                                |      |

| 6.16  | DMA Transfer End                                                                | 315 |

|-------|---------------------------------------------------------------------------------|-----|

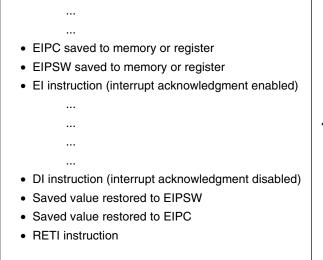

| СНАРТ | ER 7 INTERRUPT/EXCEPTION PROCESSING FUNCTION                                    | 216 |

|       |                                                                                 |     |

| 7.1   | Features                                                                        |     |

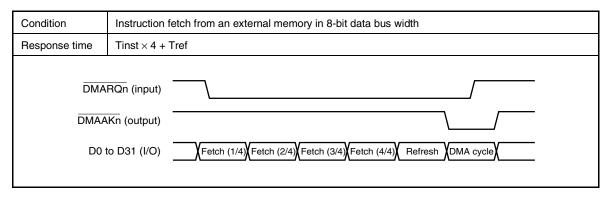

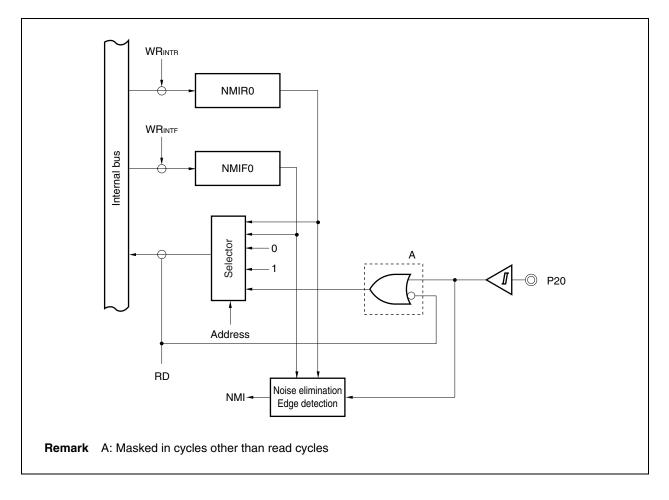

| 7.2   | Non-Maskable Interrupts                                                         |     |

|       | 7.2.1 Operation                                                                 |     |

|       | 7.2.2 Restore                                                                   |     |

|       | 7.2.3 Non-maskable interrupt status flag (NP)                                   |     |

|       | 7.2.4 Edge detection function                                                   |     |

| 7.3   | Maskable Interrupts                                                             |     |

|       | 7.3.1 Operation                                                                 |     |

|       | 7.3.2 Restore                                                                   |     |

|       | 7.3.3 Priorities of maskable interrupts                                         |     |

|       | 7.3.4 Interrupt control register (xxICn)                                        |     |

|       | 7.3.5 Interrupt mask registers 0 to 5 (IMR0 to IMR5)                            |     |

|       | 7.3.6 NMI reset status register (NRS)                                           |     |

|       | 7.3.7 In-service priority register (ISPR)                                       |     |

|       | 7.3.8 Maskable interrupt status flag (ID)                                       |     |

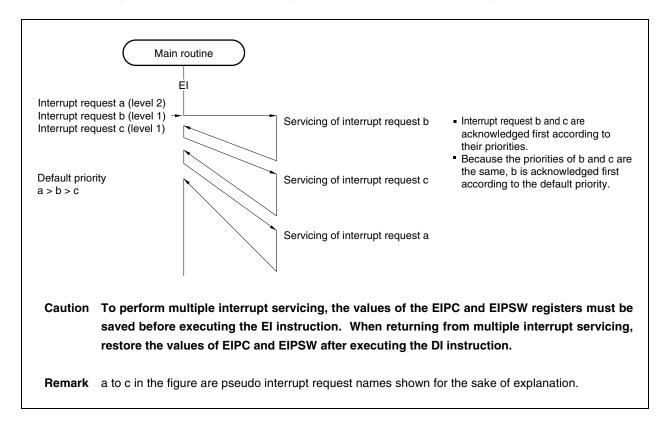

|       | 7.3.9 Selecting interrupt trigger mode                                          |     |

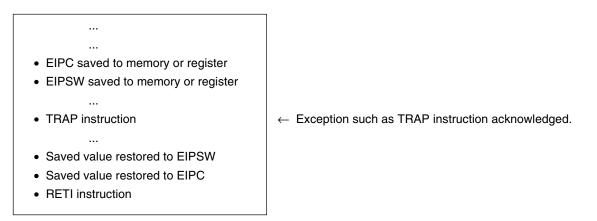

| 7.4   | Software Exception                                                              | 354 |

|       | 7.4.1 Operation                                                                 |     |

|       | 7.4.2 Restore                                                                   |     |

|       | 7.4.3 Exception status flag (EP)                                                | 356 |

| 7.5   | Exception Trap                                                                  | 357 |

|       | 7.5.1 Illegal opcode definition                                                 | 357 |

|       | 7.5.2 Debug trap                                                                |     |

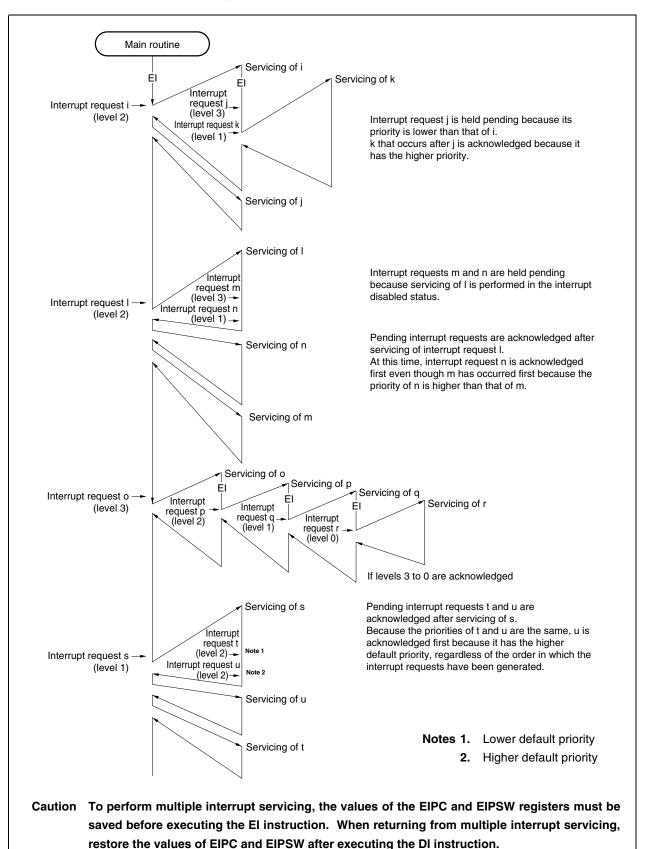

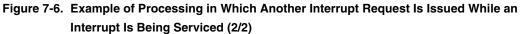

| 7.6   | Multiple Interrupt Servicing Control                                            | 361 |

| 7.7   | Interrupt Latency Time                                                          | 363 |

| 7.8   | Periods in Which Interrupts Are Not Acknowledged                                | 364 |

|       |                                                                                 |     |

|       | ER 8 CLOCK GENERATION FUNCTION                                                  |     |

| 8.1   | Features                                                                        |     |

| 8.2   | Configuration                                                                   |     |

| 8.3   | Control Registers                                                               |     |

|       | 8.3.1 Clock control register (CKC)                                              |     |

|       | 8.3.2 Clock source select register (CKS)                                        |     |

|       | 8.3.3 SSCG control register (SSCGC)                                             |     |

|       | 8.3.4 USB clock control register (UCKC)                                         |     |

|       | 8.3.5 Lock register (LOCKR)                                                     |     |

|       | 8.3.6 Oscillation stabilization time select register (OSTS)                     |     |

| 8.4   | Operation                                                                       | 376 |

|       | 8.4.1 Operation status of each clock                                            |     |

|       | 8.4.2 Setting of input clock (Fx)                                               |     |

| 8.5   | Operating Clock Provisions                                                      | 377 |

|       | 8.5.1 Calculating BUSCLK frequency                                              |     |

|       | 8.5.2 Calculating operating clock frequency of each on-chip peripheral function |     |

| 8.6   | Power-Save Control                                                              |     |

|       | 8.6.1  | Overview                                              |     |

|-------|--------|-------------------------------------------------------|-----|

|       | 8.6.2  | Control registers                                     |     |

|       | 8.6.3  | HALT mode                                             |     |

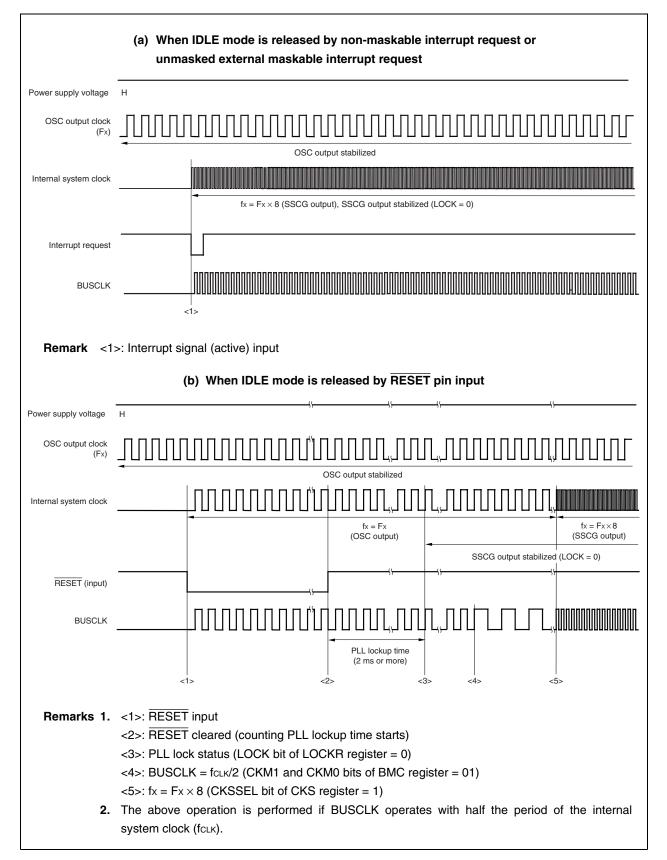

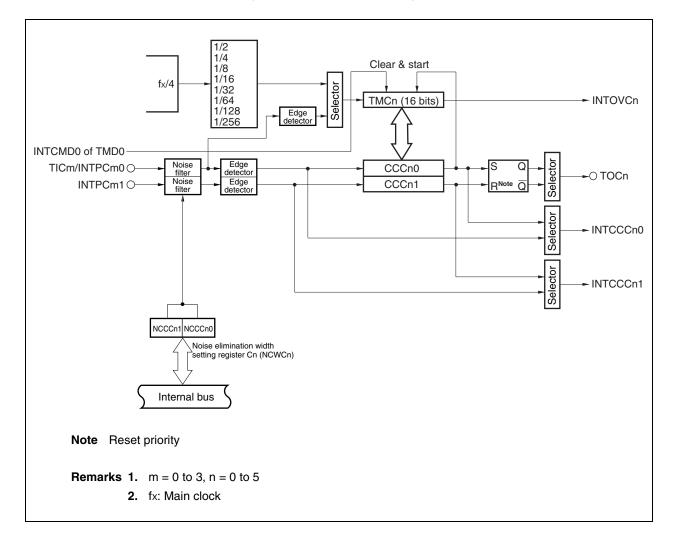

|       | 8.6.4  | IDLE mode                                             |     |

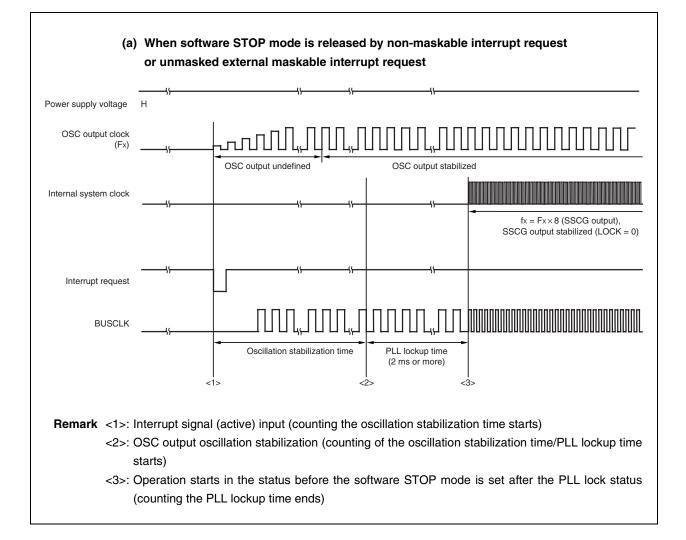

|       | 8.6.5  | Software STOP mode                                    |     |

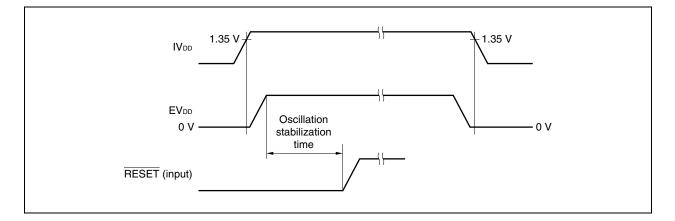

| 8.7   | Secur  | ing Oscillation Stabilization Time                    | 400 |

|       | 8.7.1  | Oscillation stabilization time security specification |     |

|       | 8.7.2  | Time base counter (TBC)                               | 400 |

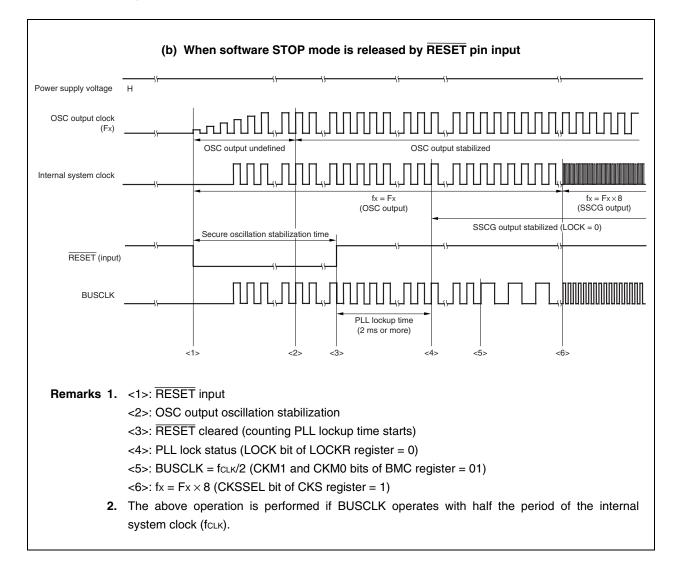

| СНАРТ | ER 9 1 | TIMER/COUNTER FUNCTION (REAL-TIME PULSE UNIT)         | 401 |

| 9.1   | Timer  | C                                                     | 401 |

|       | 9.1.1  | Features                                              | 401 |

|       | 9.1.2  | Function overview                                     | 401 |

|       | 9.1.3  | Basic configuration                                   | 402 |

|       | 9.1.4  | Timer C                                               | 404 |

|       | 9.1.5  | Control registers                                     | 408 |

|       | 9.1.6  | Operation                                             | 416 |

|       | 9.1.7  | Application examples                                  | 423 |

|       | 9.1.8  | Cautions                                              | 430 |

| 9.2   | Timer  | <sup>•</sup> D                                        | 431 |

|       | 9.2.1  | Features                                              | 431 |

|       | 9.2.2  | Function overview                                     | 431 |

|       | 9.2.3  | Basic configuration                                   | 431 |

|       | 9.2.4  | Timer D                                               | 432 |

|       | 9.2.5  | Control registers                                     | 435 |

|       | 9.2.6  | Operation                                             | 437 |

|       | 9.2.7  | Application examples                                  | 439 |

|       | 9.2.8  | Cautions                                              | 439 |

| 9.3   | Timer  | ENC1                                                  | 440 |

|       | 9.3.1  | Features                                              | 440 |

|       | 9.3.2  | Function overview                                     | 440 |

|       | 9.3.3  | Basic configuration                                   |     |

|       | 9.3.4  | Timer ENC1                                            |     |

|       | 9.3.5  | Control registers                                     |     |

|       | 9.3.6  | Operation                                             |     |

|       | 9.3.7  | Supplementary description of internal operation       | 472 |

| СНАРТ | ER 10  | SERIAL INTERFACE FUNCTION                             |     |

|       |        | res                                                   |     |

| 10.1  | 10.1.1 | Switching between UARTB0 and CSI30 modes              |     |

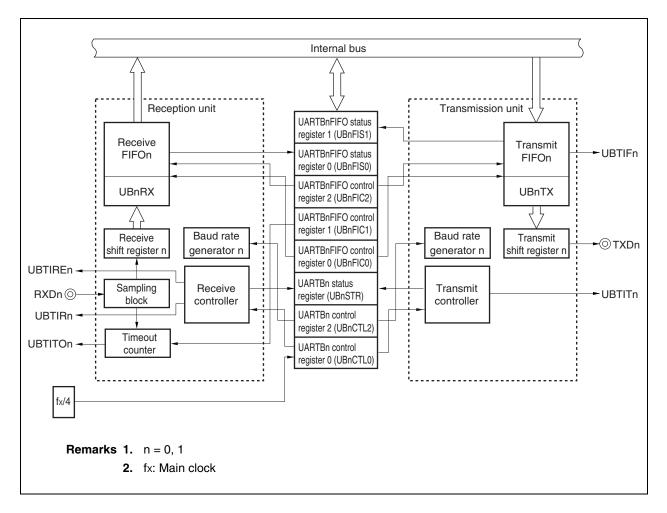

| 10 2  | -      | chronous Serial Interfaces B0, B1 (UARTB0, UARTB1)    |     |

| 10.2  | 10.2.1 | Features                                              |     |

|       | 10.2.1 | Configuration                                         |     |

|       | 10.2.2 | Control registers                                     |     |

|       | 10.2.3 | Interrupt requests                                    |     |

|       | 10.2.4 | Control method                                        |     |

|       | 10.2.5 |                                                       |     |

|       | 10.2.0 |                                                       |     |

|        | 10.2.7 Dedicated baud rate generators 0, 1 (BRG0, BRG1)     | 516 |

|--------|-------------------------------------------------------------|-----|

|        | 10.2.8 Control flow                                         |     |

|        | 10.2.9 Cautions                                             |     |

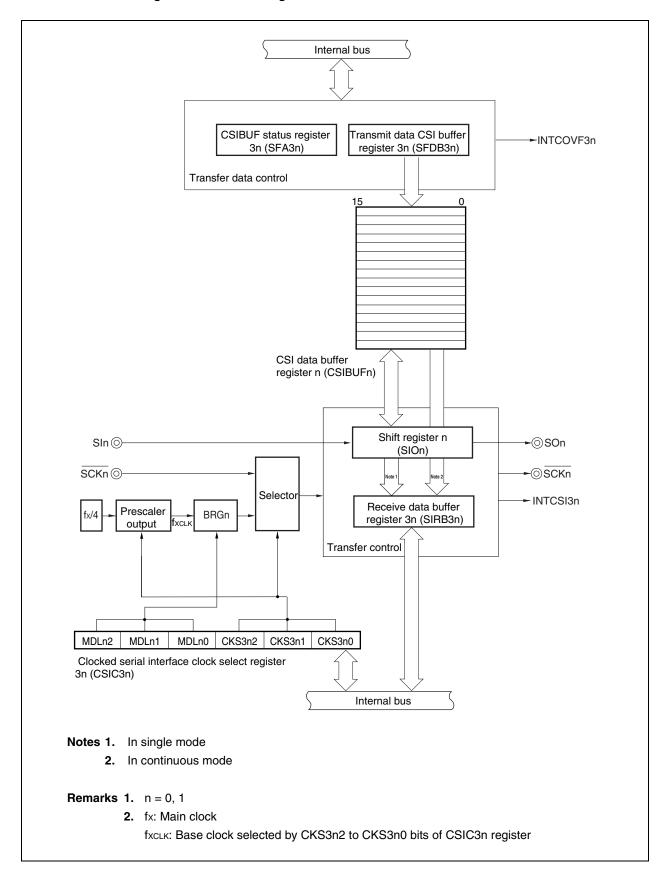

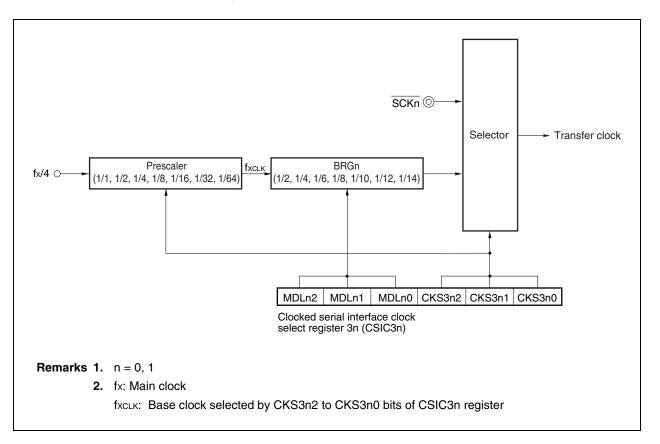

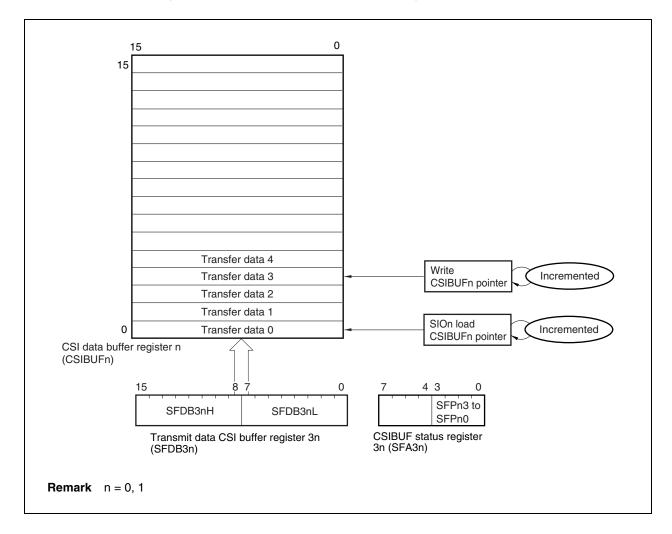

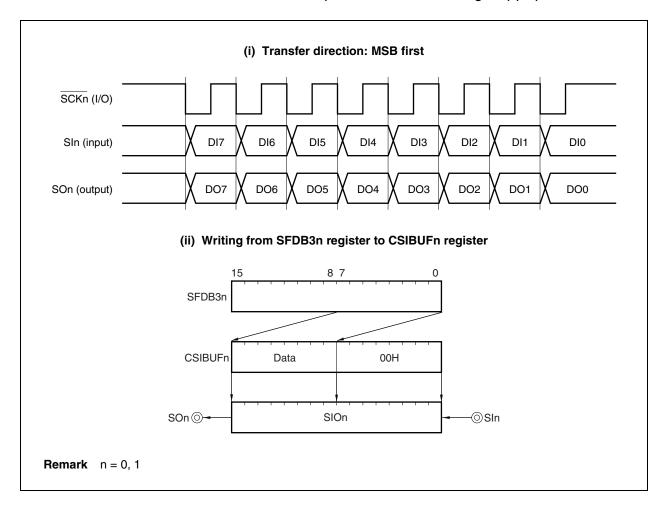

| 10.3   | Clocked Serial Interfaces 30, 31 (CSI30, CSI31)             | 533 |

|        | 10.3.1 Features                                             |     |

|        | 10.3.2 Configuration                                        | 534 |

|        | 10.3.3 Control registers                                    | 536 |

|        | 10.3.4 Dedicated baud rate generators 0, 1 (BRG0, BRG1)     | 548 |

|        | 10.3.5 Operation                                            | 550 |

|        | 10.3.6 Usage                                                |     |

|        | 10.3.7 Cautions                                             | 574 |

| СНАРТЕ | ER 11 USB FUNCTION CONTROLLER (USBF)                        | 575 |

| 11.1   | Overview                                                    |     |

| 11.2   | Configuration                                               |     |

| 11.3   | Requests                                                    | 577 |

|        | 11.3.1 Automatic requests                                   |     |

|        | 11.3.2 Other requests                                       |     |

| 11.4   | Register Configuration                                      | 586 |

|        | 11.4.1 Control registers                                    |     |

|        | 11.4.2 Data hold registers                                  | 639 |

|        | 11.4.3 Request data register area                           |     |

|        | 11.4.4 Peripheral control registers                         |     |

| 11.5   | STALL Handshake or No Handshake                             | 682 |

| 11.6   | Register Values in Specific Status                          |     |

| 11.7   | FW Processing                                               | 685 |

|        | 11.7.1 Initialization processing                            |     |

|        | 11.7.2 Interrupt servicing                                  | 690 |

|        | 11.7.3 USB main processing                                  | 691 |

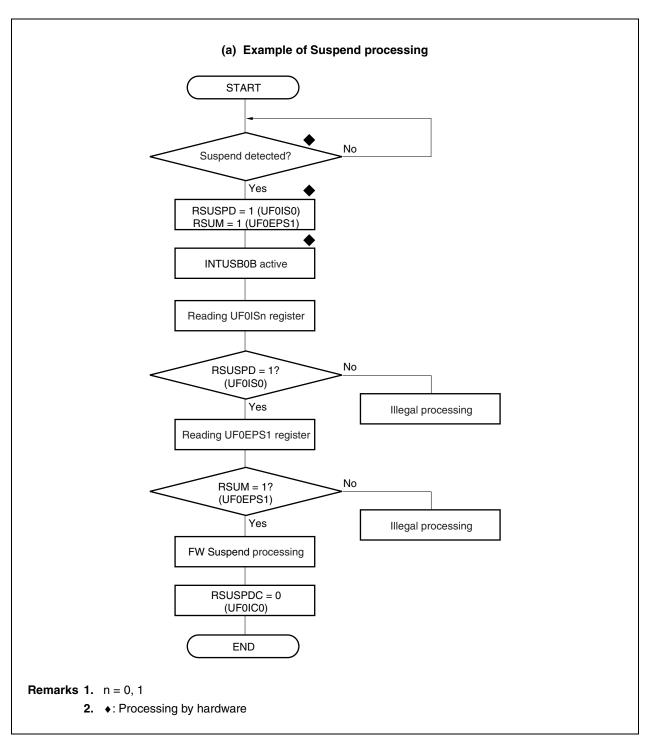

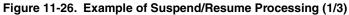

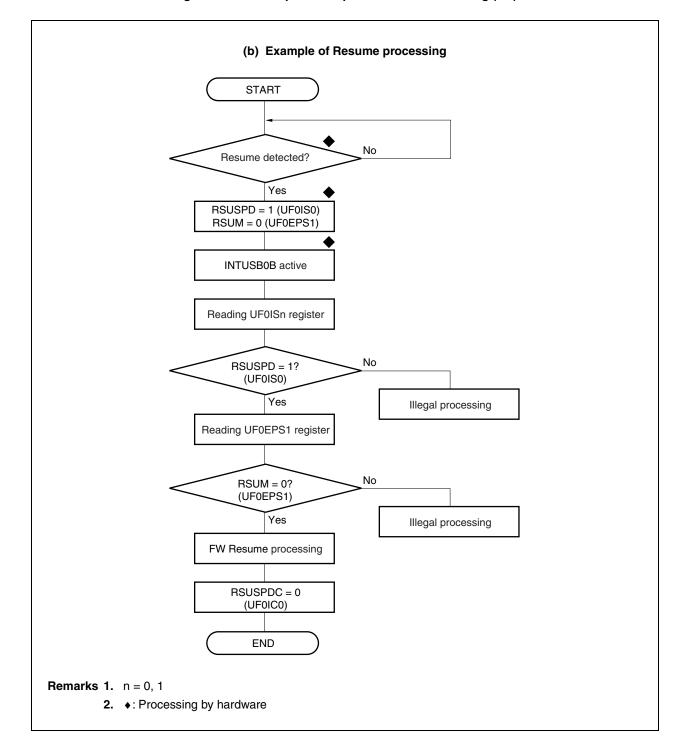

|        | 11.7.4 Suspend/Resume processing                            | 718 |

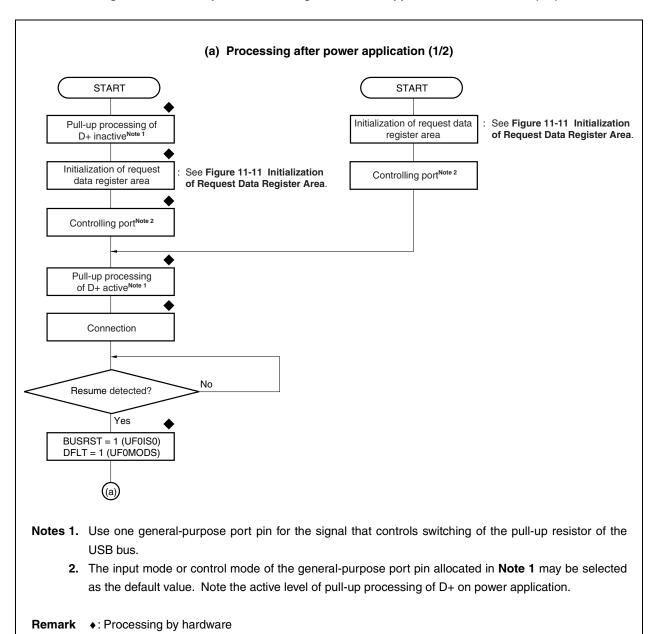

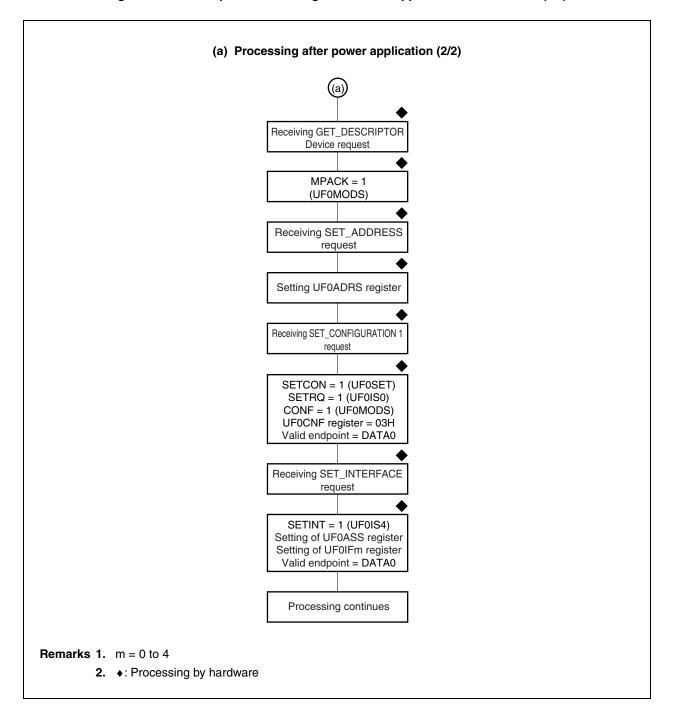

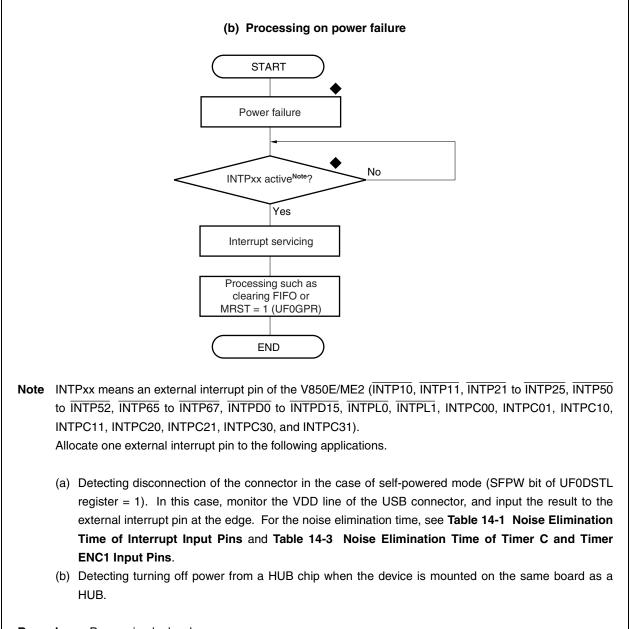

|        | 11.7.5 Processing after power application                   | 721 |

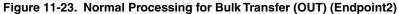

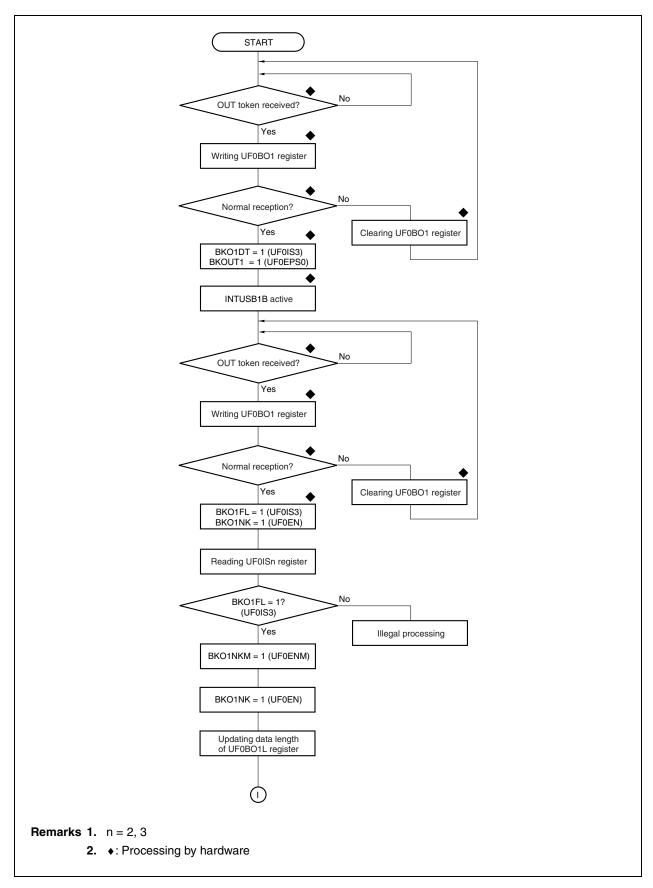

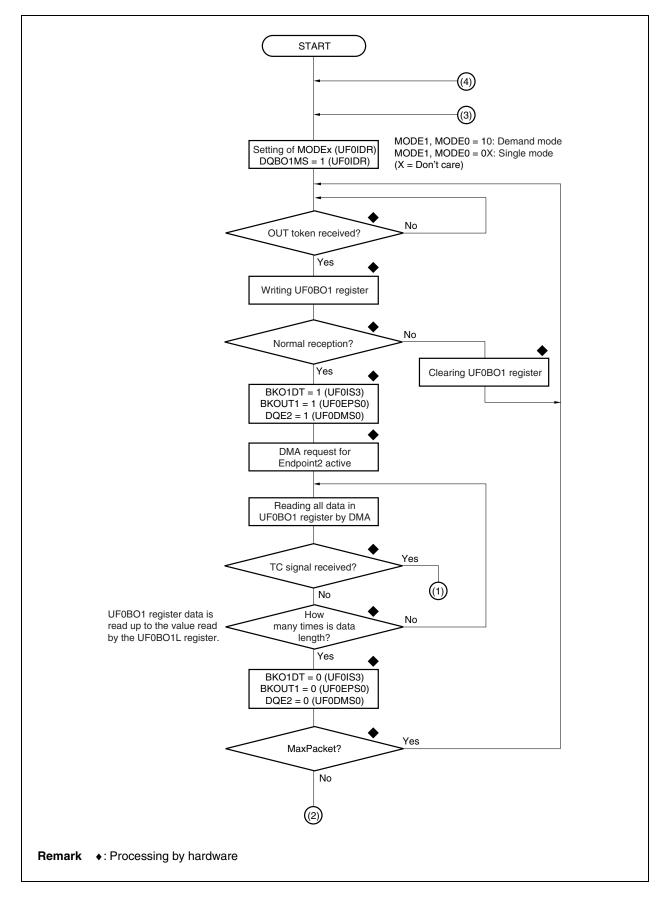

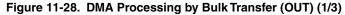

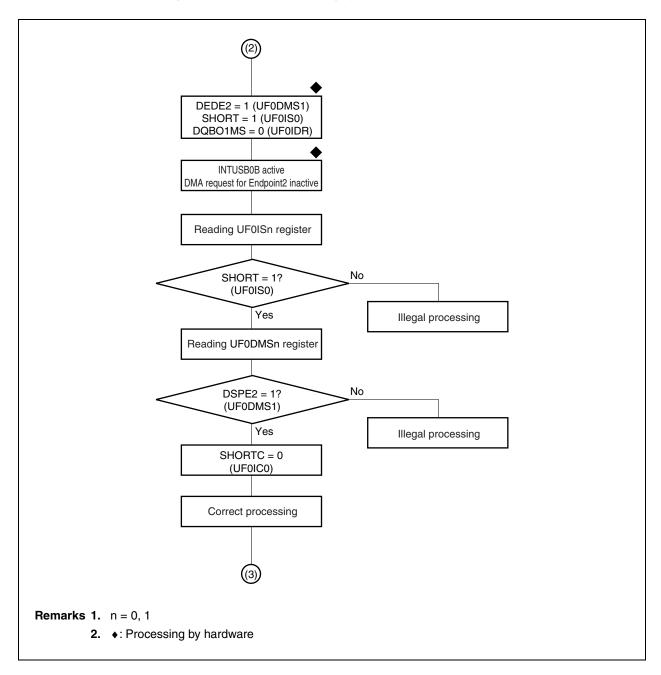

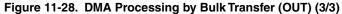

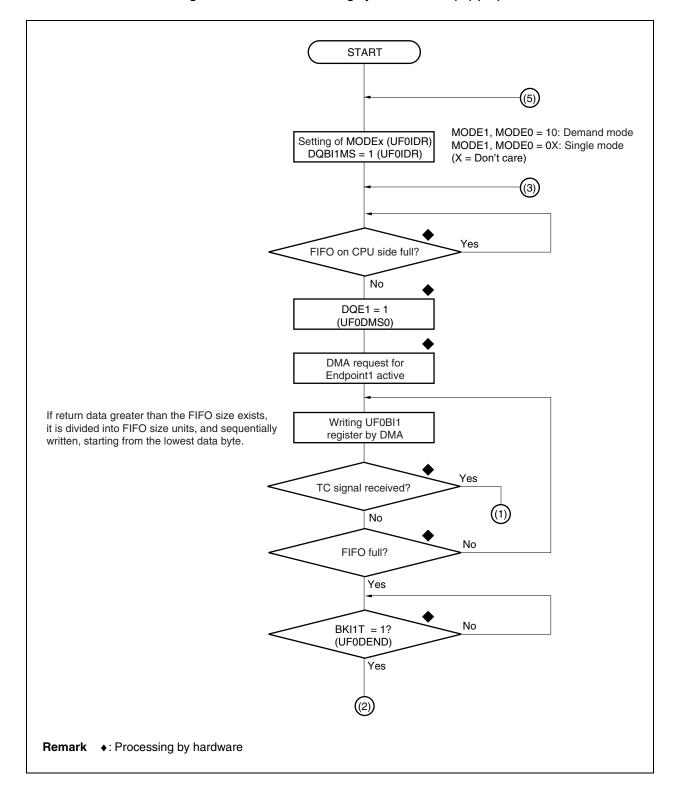

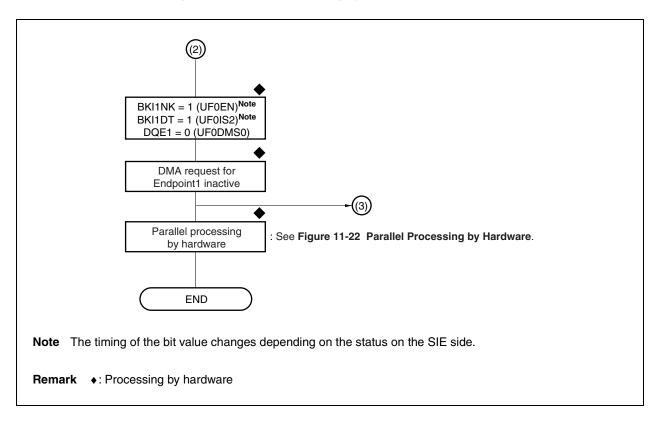

|        | 11.7.6 Receiving data for bulk transfer (OUT) in DMA mode   |     |

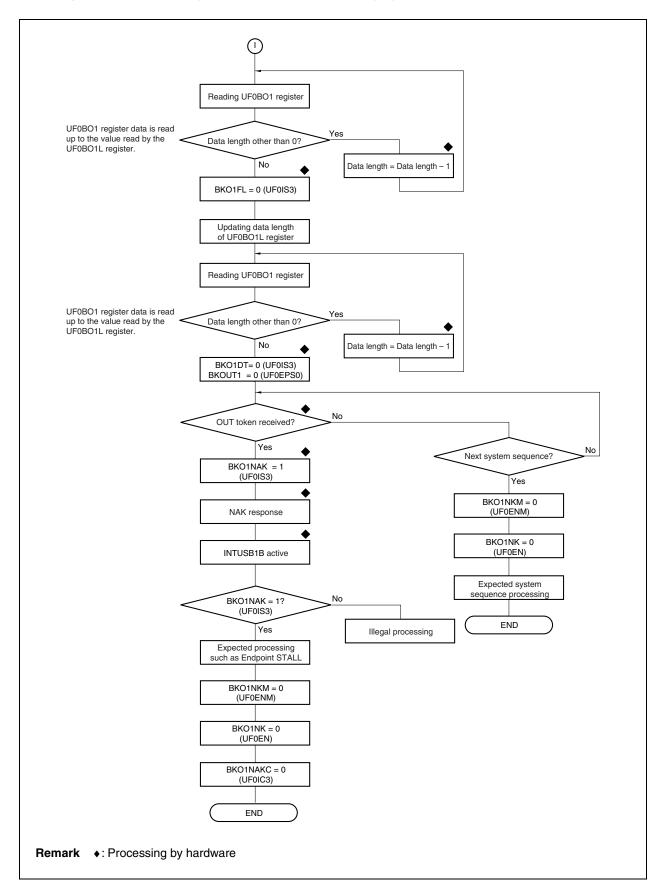

|        | 11.7.7 Transmitting data for bulk transfer (IN) in DMA mode |     |

|        | 11.7.8 USB connection example                               | 733 |

| СНАРТЕ | ER 12 A/D CONVERTER                                         | 734 |

| 12.1   | Features                                                    | 734 |

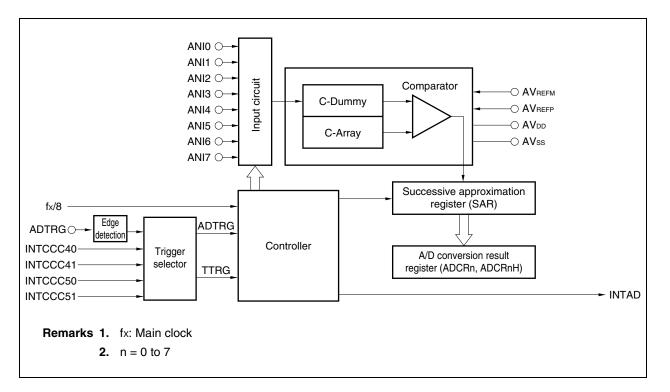

|        | Configuration                                               |     |

|        | Control Registers                                           |     |

| 12.4   | Operation                                                   |     |

|        | 12.4.1 Basic operation                                      |     |

|        | 12.4.2 Operation mode and trigger mode                      |     |

| 12.5   | Operation in A/D Trigger Mode                               |     |

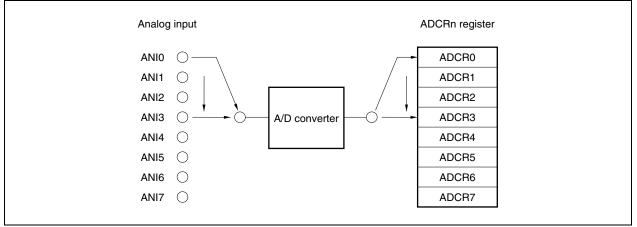

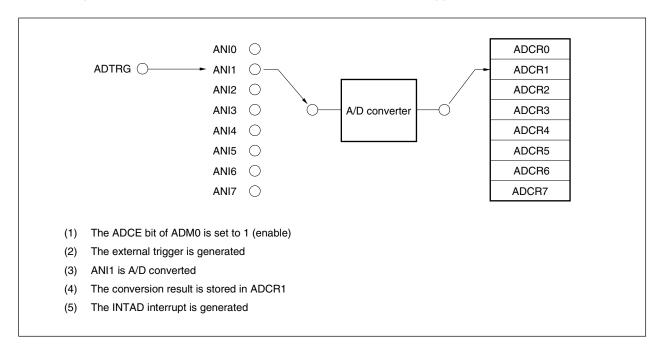

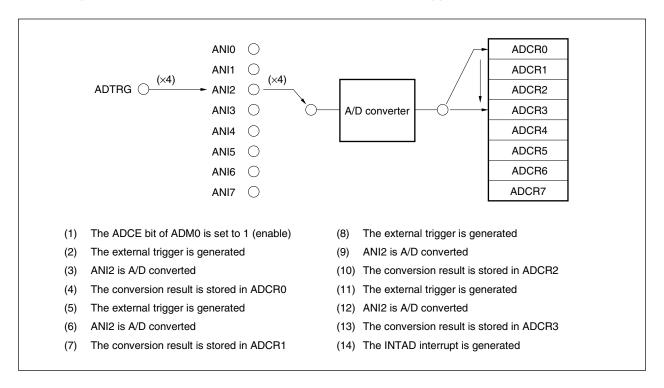

|        | 12.5.1 Select mode operation                                |     |

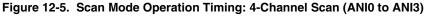

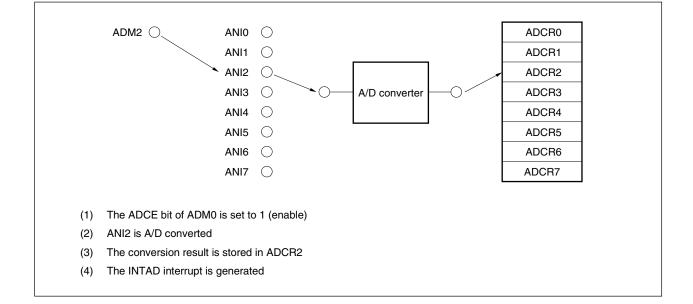

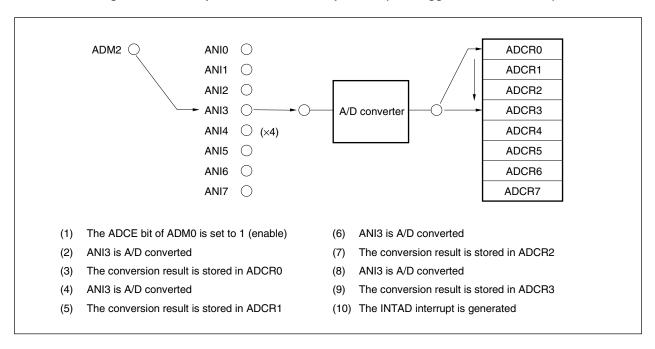

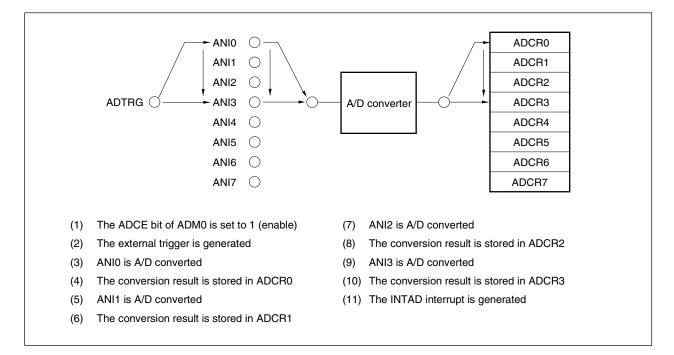

|        | 12.5.2 Scan mode operations                                 |     |

| 12.6   | Operation in Timer Trigger Mode                             |     |

|        | 12.6.1 Select mode operation                                |     |

|        |                                                             |     |

$\star$

|        | 12.6.2   | Scan mode operation                                 | 756 |

|--------|----------|-----------------------------------------------------|-----|

| 12.7   | Operat   | ion in External Trigger Mode                        | 757 |

|        | 12.7.1   | Select mode operations                              | 757 |

|        | 12.7.2   | Scan mode operation                                 | 760 |

| 12.8   | Notes of | on Operation                                        | 761 |

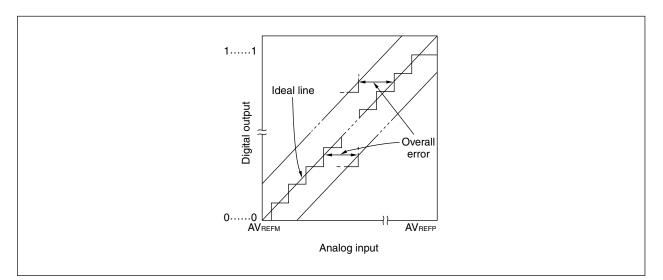

| * 12.9 | How to   | Read A/D Converter Characteristics Table            | 763 |

|        |          |                                                     |     |

| CHAPTE | ER 13    | PWM UNIT                                            | 767 |

|        |          | es                                                  |     |

|        | -        | uration                                             |     |

|        |          | I Registers                                         |     |

| 13.4   | Operat   | ion                                                 |     |

|        | 13.4.1   | PWM basic operation                                 |     |

|        | 13.4.2   | Starting/stopping PWM operation                     |     |

|        | 13.4.3   | Setting active level of PWM pulse                   |     |

|        | 13.4.4   | Specifying PWM pulse width rewrite period           | 778 |

|        | 13.4.5   | Repeat cycle                                        | 779 |

|        |          | PORT FUNCTIONS                                      | 700 |

|        |          | PORT FUNCTIONS                                      |     |

|        |          | es                                                  |     |

|        |          | onfiguration                                        |     |

| 14.3   |          | n Functions                                         |     |

|        | 14.3.1   | Port 1                                              |     |

|        | 14.3.2   | Port 2                                              |     |

|        | 14.3.3   | Port 5                                              |     |

|        | 14.3.4   | Port 6                                              |     |

|        | 14.3.5   | Port 7                                              |     |

|        | 14.3.6   | Port AL                                             |     |

|        | 14.3.7   | Port AH                                             | 837 |

|        | 14.3.8   | Port DH                                             | 839 |

|        | 14.3.9   | Port CS                                             | 848 |

|        | 14.3.10  | Port CT                                             | 851 |

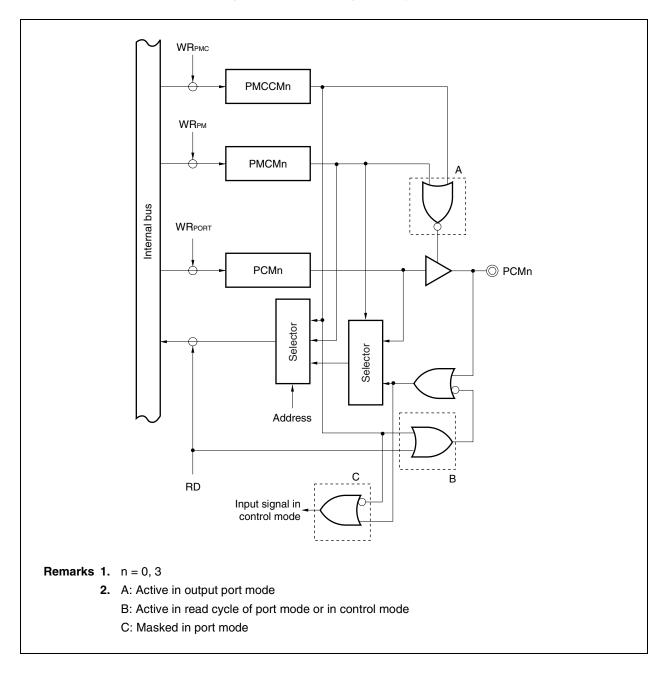

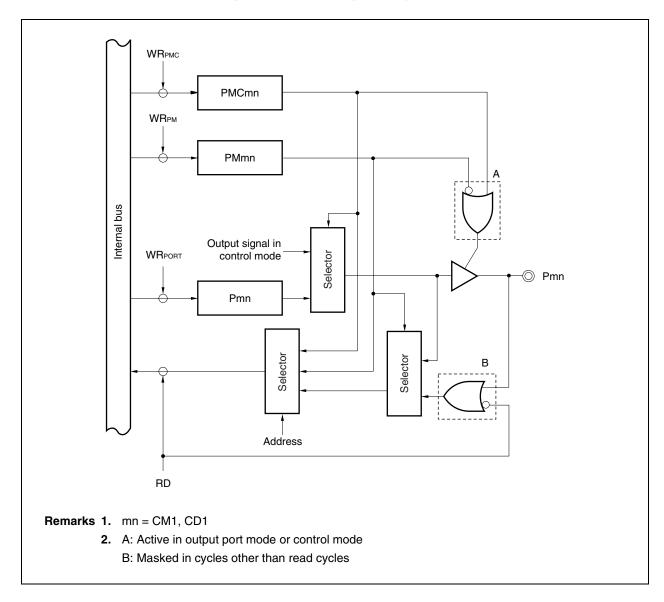

|        | 14.3.11  | Port CM                                             | 854 |

|        | -        | Port CD                                             |     |

|        |          | uration of RESET, A2 to A15, and D0 to D15 Pins     |     |

| 14.5   | Operat   | ion of Port Function                                | 861 |

|        | 14.5.1   | Writing to I/O port                                 |     |

|        | 14.5.2   | Reading from I/O port                               |     |

|        | 14.5.3   | Output status of alternate function in control mode |     |

| 14.6   | Noise I  | Eliminator                                          |     |

|        | 14.6.1   | Interrupt input pin                                 | 862 |

|        | 14.6.2   | A/D converter input pin                             |     |

|        | 14.6.3   | Timer C and timer ENC1 input pins                   |     |

| 01115  |          |                                                     |     |

|        |          | RESET FUNCTIONS                                     |     |

| 15.1   | Overvi   | ew                                                  | 867 |

|   | 15.2 Configuration                                   |     |

|---|------------------------------------------------------|-----|

|   | 15.3 Operation                                       | 868 |

|   | 15.4 Initialization                                  |     |

|   | CHAPTER 16 DEBUG FUNCTION (DCU)                      | 879 |

|   | 16.1 Functional Outline                              | 879 |

|   | 16.1.1 Debug function                                |     |

|   | 16.1.2 Trace function                                |     |

|   | 16.1.3 Event function                                |     |

|   | 16.2 Connection with N-Wire Type IE                  |     |

|   | 16.2.1 IE connector (on target system side)          |     |

|   | 16.2.2 Recommended circuit example                   |     |

| * | CHAPTER 17 ELECTRICAL SPECIFICATIONS (TARGET VALUES) |     |

| * | CHAPTER 18 PACKAGE DRAWING                           | 928 |

| * | CHAPTER 19 RECOMMENDED SOLDERING CONDITIONS          | 929 |

|   | APPENDIX A REGISTER INDEX                            | 930 |

|   | APPENDIX B INSTRUCTION SET LIST                      | 943 |

|   | B.1 Conventions                                      |     |

|   | B.2 Instruction Set (in Alphabetical Order)          |     |

| * | APPENDIX C REVISION HISTORY                          | 953 |

# LIST OF FIGURES (1/6)